www.ti.com

EMAC Port Registers

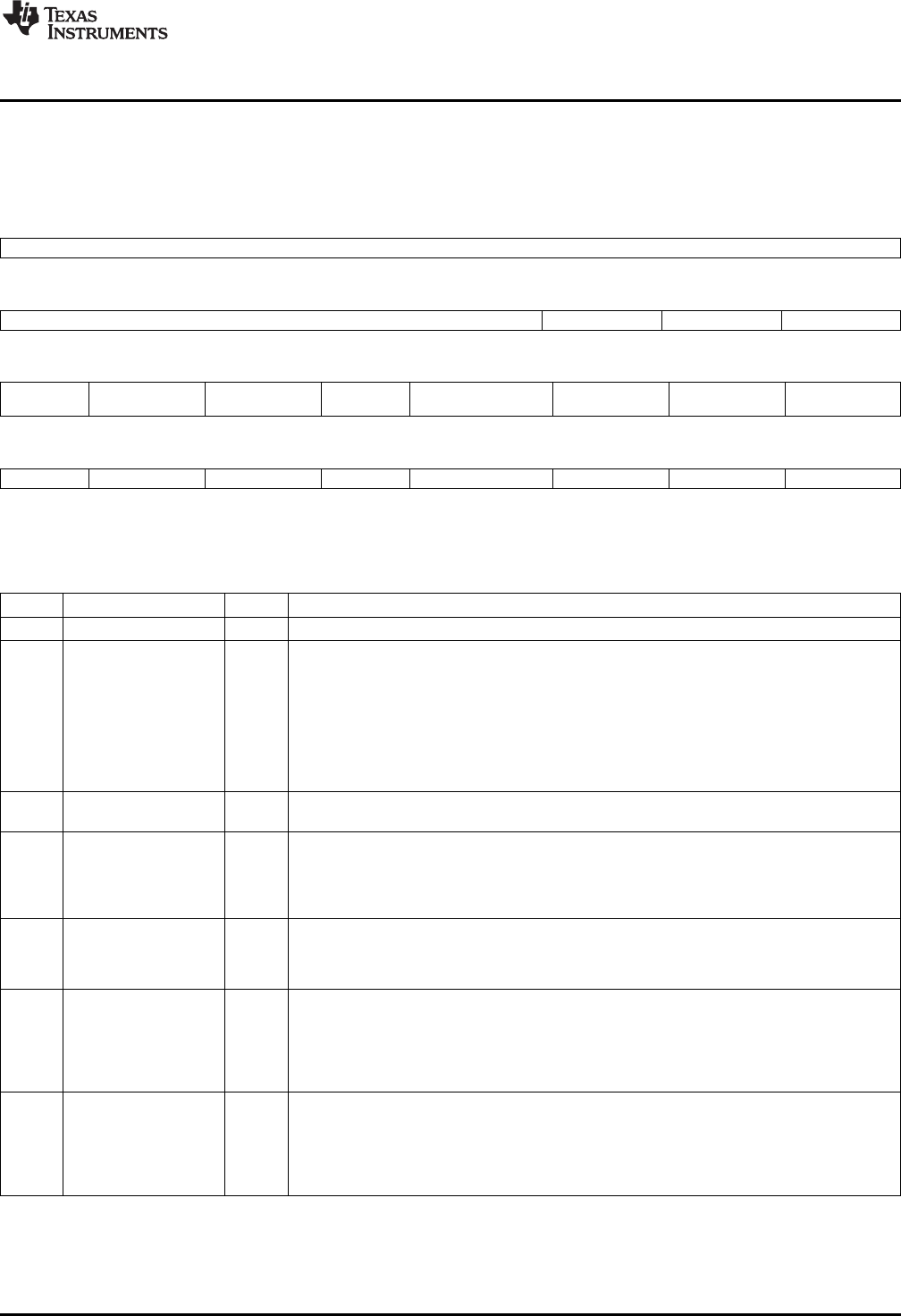

5.29 MAC Control Register (MACCONTROL)

The MAC control register (MACCONTROL) is shown in Figure 71 and described in Table 65.

Figure 71. MAC Control Register (MACCONTROL)

31 24

Reserved

R-0

23 19 18 17 16

Reserved RGMIIEN GIGFORCE RMIIDUPLEXMODE

R-0 R/W-0 R/W-0 R/W-0

15 14 13 12 11 10 9 8

RXFIFO

RMIISPEED RXOFFLENBLOCK RXOWNERSHIP CMDIDLE Reserved TXPTYPE Reserved

FLOWEN

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R-0 R/W-0 R-0

7 6 5 4 3 2 1 0

GIG TXPACE GMIIEN TXFLOWEN RXBUFFERFLOWEN Reserved LOOPBACK FULLDUPLEX

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 65. MAC Control Register (MACCONTROL) Field Descriptions

Bit Field Value Description

31-19 Reserved 0 Reserved

18 RGMIIEN RGMII enable bit. Enables the fullduplex and gigabit mode to be selected from the

RGMIIFULLDUPLEX and RGMIIGIG input signals and not from the FULLDUPLEX and GIG

bits contained in this register. This bit is directly connected to the RXINBAND input on the

RGMII module.

0 The RGMII interface is in forced link mode. The duplexity is determined by the FULLDUPLEX

bit, and the speed is determined by the GIG bit. The speed is either 1 Gbps or 100 Mbps; 10

Mbps is not supported in forced link mode.

1 The RGMII interface requires and uses the in-band signals coming in on its receive.

17 GIGFORCE Gigabit force mode. This bit is used to force the EMAC into gigabit mode if the input MTCLK

signal has been stopped by the PHY.

16 RMIIDUPLEXMODE Duplex mode for the RMII interface.

0 The RMII operates in half-duplex mode. This mode is not supported in the TCI6486/C6472

devices.

1 The RMII operates in full-duplex mode.

15 RMIISPEED Operating speed for the RMII interface

0 The RMII operates at 2.5 MHz (10Mbps mode)

1 The RMII operates at 25 MHz (100 Mbps mode)

14 RXOFFLENBLOCK Receive offset / length word write block

0 Do not block the DMA writes to the receive buffer descriptor offset/buffer length word

1 Block all EMAC DMA controller writes to the receive buffer descriptor offset/buffer length

words during packet processing. When this bit is set, the EMAC will never write the third word

to any receive buffer descriptor.

13 RXOWNERSHIP Receive ownership write bit value

0 The EMAC writes the Receive ownership bit to zero at the end-of-packet processing

1 The EMAC writes the Receive ownership bit to one at the end-of-packet processing. If you do

not use the ownership mechanism, you can set this mode to preclude the necessity of

software having to set this bit each time the buffer descriptor is used.

125

SPRUEF8F–March 2006–Revised November 2010 C6472/TCI6486 EMAC/MDIO

Submit Documentation Feedback

Copyright © 2006–2010, Texas Instruments Incorporated