MuxOneNAND2G(KFM2G16Q2A-DEBx)

- 134 -

FLASH MEMORY

MuxOneNAND4G(KFN4G16Q2A-DEBx)

3.16 DQ6 Toggle Bit

The MuxOneNAND device has DQ6 Toggle bit. Toggle bit is another option to detect whether an internal load operation is in progress or com-

pleted. Once the BufferRAM(BootRAM, DataRAM0, DataRAM1) is at a busy state during internal load operation, DQ6 will toggle. Toggling

DQ6 will stop after the device completes its internal load operation. The MuxOneNAND device’s DQ6 Toggle will be valid only when host

reads BufferRAM designated by BSA which will be loaded by internal load operation. DQ6 toggle can be used 350ns after load com-

mand(0000h and 0013h of Command based Operation) issue, until data sensing from the NAND Flash Array memory into Page Buffer and

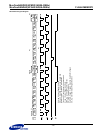

transferring from the Page Buffer to the DataRAM are finished. By reading the same address more than twice utilizing asynchronous (Figure

6.22, 6.23), the host will read toggled value of DQ6 and the rest of DQ’s are not guaranteed to be fixed value. DQ6 toggle is only for reading

status of BufferRAM which is being loaded by internal operation, that is, BufferRAM designated by BSA. Host may read previous data from

BufferRAM not pointed by BSA during internal load operation. DQ6 toggle bit is read at the address, 0000~000Fh for BootRAM, 200~21Fh for

DataRAM0, or 600~61Fh for DataRAM1, by asynchronous read.

DQ6 toggle bit can be useful at Cold Reset to determine the ready/busy state of MuxOneNAND. Since INT pin is initially at High-Z state, when

host needs to check the completion of bootcode copy operation, the host cannot judge the ready/busy status of MuxOneNAND by INT pin.

Therefore, by checking DQ6 toggle of BootRAM, the host should detect the completion of bootcode copy.

Note that DQ6 toggle bit is not valid at Cache Read and Synchronous Burst Block Read.

Status DQ15~DQ7 DQ6 DQ5~DQ0

In Progress Data Loading X (Don’t Care) Toggle X (Don’t Care)