Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 106 SMSC LAN9311/LAN9311i

DATASHEET

8.5.3 Special Restrictions on Back-to-Back Read Cycles

There are also restrictions on specific back-to-back host read operations. These restrictions concern

reading specific registers after reading a resource that has side effects. In many cases there is a delay

between reading the LAN9311/LAN9311i, and the subsequent indication of the expected change in the

control and status register values.

In order to prevent the host from reading stale data on back-to-back reads, minimum wait periods have

been established. These periods are specified in Table 8.2. The host processor is required to wait the

specified period of time between read operations of specific combinations of resources. The wait period

is dependant upon the combination of registers being read.

Performing “dummy” reads of the Byte Order Test Register (BYTE_TEST) register is a convenient way

to guarantee that the minimum wait time restriction is met. Ta ble 8. 2 below also shows the number of

dummy reads that are required for back-to-back read operations. The number of BYTE_TEST reads

in this table is based on the minimum timing for T

cyc

(45ns). For microprocessors with slower busses

the number of reads may be reduced as long as the total time is equal to, or greater than the time

specified in the table. Dummy reads of the BYTE_TEST register are not required as long as the

minimum time period is met.

Note 8.1 This timing applies only to the auto-increment and auto-decrement modes of Switch Fabric

CSR register access.

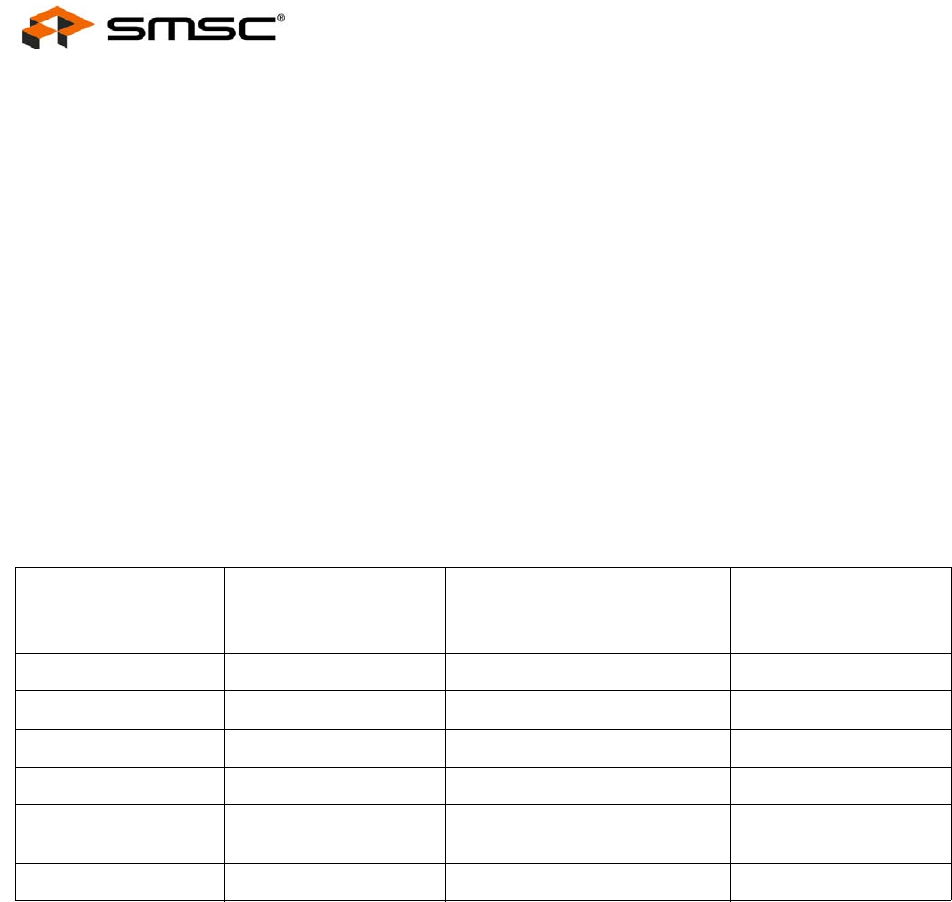

Table 8.2 Read After Read Timing Rules

AFTER READING...

WAIT FOR THIS MANY

NANOSECONDS...

OR PERFORM THIS MANY

READS OF BYTE_TEST…

(ASSUMING T

CYC

OF 45NS) BEFORE READING...

RX Data FIFO 135 3 RX_FIFO_INF

RX Status FIFO 135 3 RX_FIFO_INF

TX Status FIFO 135 3 TX_FIFO_INF

RX_DROP 180 4 RX_DROP

SWITCH_CSR_DATA 45 1 SWITCH_CSR_CMD

Note 8.1

VPHY_AN_EXP 45 1 VPHY_AN_EXP