Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 16 SMSC LAN9311/LAN9311i

DATASHEET

Chapter 1 Preface

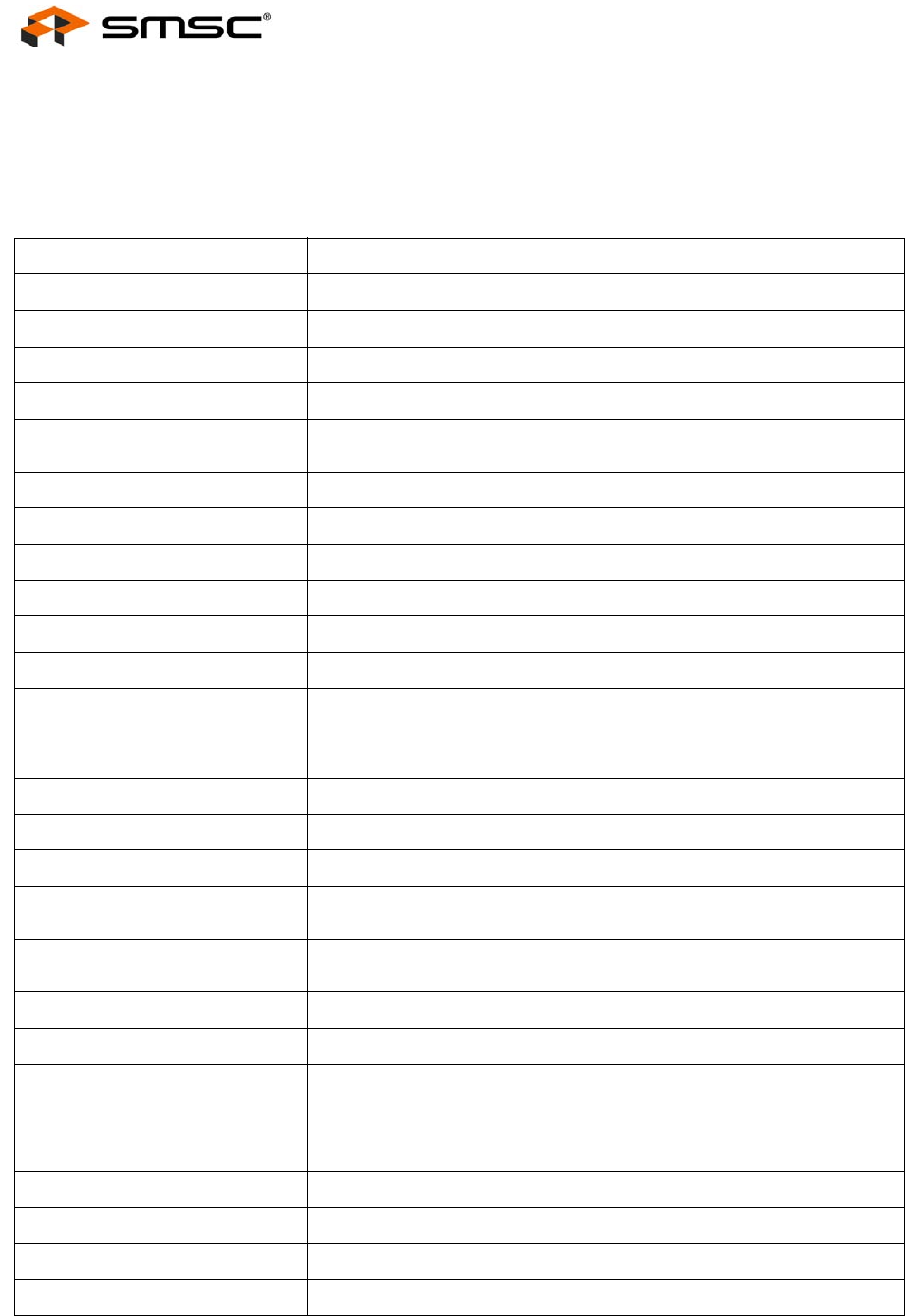

1.1 General Terms

100BT 100BASE-T (100Mbps Fast Ethernet, IEEE 802.3u)

ADC Analog-to-Digital Converter

ALR Address Logic Resolution

BLW Baseline Wander

BM Buffer Manager - Part of the switch fabric

BPDU Bridge Protocol Data Unit - Messages which carry the Spanning Tree

Protocol information

Byte 8-bits

CSMA/CD Carrier Sense Multiple Access / Collision Detect

CSR Control and Status Registers

CTR Counter

DA Destination Address

DWORD 32-bits

EPC EEPROM Controller

FCS Frame Check Sequence - The extra checksum characters added to the end

of an Ethernet frame, used for error detection and correction.

FIFO First In First Out buffer

FSM Finite State Machine

GPIO General Purpose I/O

HBI Host Bus Interface. The physical bus connecting the LAN9311/LAN9311i to

the host. Also referred to as the Host Bus.

HBIC Host Bus Interface Controller. The hardware module that interfaces

theLAN9311/LAN9311i to the HBI.

Host External system (Includes processor, application software, etc.)

IGMP Internet Group Management Protocol

Inbound Refers to data input to the LAN9311/LAN9311i from the host

Level-Triggered Sticky Bit This type of status bit is set whenever the condition that it represents is

asserted. The bit remains set until the condition is no longer true, and the

status bit is cleared by writing a zero.

lsb Least Significant Bit

LSB Least Significant Byte

MDI Medium Dependant Interface

MDIX Media Independent Interface with Crossover