Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 176 SMSC LAN9311/LAN9311i

DATASHEET

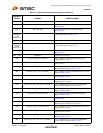

19 GP Timer (GPT_INT)

This interrupt is issued when the General Purpose Timer Count Register

(GPT_CNT) wraps past zero to FFFFh.

R/WC 0b

18

RESERVED RO -

17

Power Management Interrupt Event (PME_INT)

This interrupt is issued when a Power Management Event is detected as

configured in the Power Management Control Register (PMT_CTRL). This

interrupt functions independent of the PME signal, and will still function if

the PME signal is disabled. Writing a '1' clears this bit regardless of the

state of the PME hardware signal. In order to clear this bit, all unmasked

bits in the Power Management Control Register (PMT_CTRL) must first be

cleared.

Note: The Interrupt De-assertion interval does not apply to the PME

interrupt.

R/WC 0b

16

TX Status FIFO Overflow (TXSO)

This interrupt is generated when the TX Status FIFO overflows.

R/WC 0b

15

Receive Watchdog Time-out (RWT)

This interrupt is generated when a packet larger than 2048 bytes has been

received by the Host MAC.

Note: This can occur when the switch engine adds a tag to a non-tagged

jumbo packet that is originally larger than 2044 bytes.

R/WC 0b

14

Receiver Error (RXE)

Indicates that the Host MAC receiver has encountered an error. Please

refer to Section 9.9.5, "Receiver Errors," on page 137 for a description of

the conditions that will cause an RXE.

R/WC 0b

13

Transmitter Error (TXE)

When generated, indicates that the Host MAC transmitter has encountered

an error. Please refer to Section 9.8.7, "Transmitter Errors," on page 132

for a description of the conditions that will cause a TXE.

R/WC 0b

12

GPIO Interrupt Event (GPIO)

This bit indicates an interrupt event from the General Purpose I/O. The

source of the interrupt can be determined by polling the General Purpose

I/O Interrupt Status and Enable Register (GPIO_INT_STS_EN)

RO 0b

11

RESERVED RO -

10

TX Data FIFO Overrun Interrupt (TDFO)

This interrupt is generated when the TX Data FIFO is full, and another write

is attempted.

R/WC 0b

9

TX Data FIFO Available Interrupt (TDFA)

This interrupt is generated when the TX Data FIFO available space is

greater than the programmed level in the TX Data Available Level field of

the FIFO Level Interrupt Register (FIFO_INT).

R/WC 0b

8

TX Status FIFO Full Interrupt (TSFF)

This interrupt is generated when the TX Status FIFO is full.

R/WC 0b

7

TX Status FIFO Level Interrupt (TSFL)

This interrupt is generated when the TX Status FIFO reaches the

programmed level in the TX Status Level field of the FIFO Level Interrupt

Register (FIFO_INT).

R/WC 0b

6

RX Dropped Frame Interrupt (RXDF_INT)

This interrupt is issued whenever a receive frame is dropped by the Host

MAC.

R/WC 0b

5

RESERVED RO -

BITS DESCRIPTION TYPE DEFAULT