Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 271 Revision 1.4 (08-19-08)

DATASHEET

14.3 Host MAC Control and Status Registers

This section details the Host MAC System CSR’s. These registers are located in the Host MAC and

are accessed indirectly via the HBI system CSR’s. Table 14.6 lists Host MAC registers that are

accessible through the indexing method using the Host MAC CSR Interface Command Register

(MAC_CSR_CMD) and Host MAC CSR Interface Data Register (MAC_CSR_DATA).

The Host MAC registers allow configuration of the various Host MAC parameters including the Host

MAC address, flow control, multicast hash table, and wake-up configuration. The Host MAC CSR’s

also provide serial access to the PHYs via the registers HMAC_MII_ACC and HMAC_MII_DATA.

These registers allow access to the 10/100 Ethernet PHY registers and the switch engine (via Port 0).

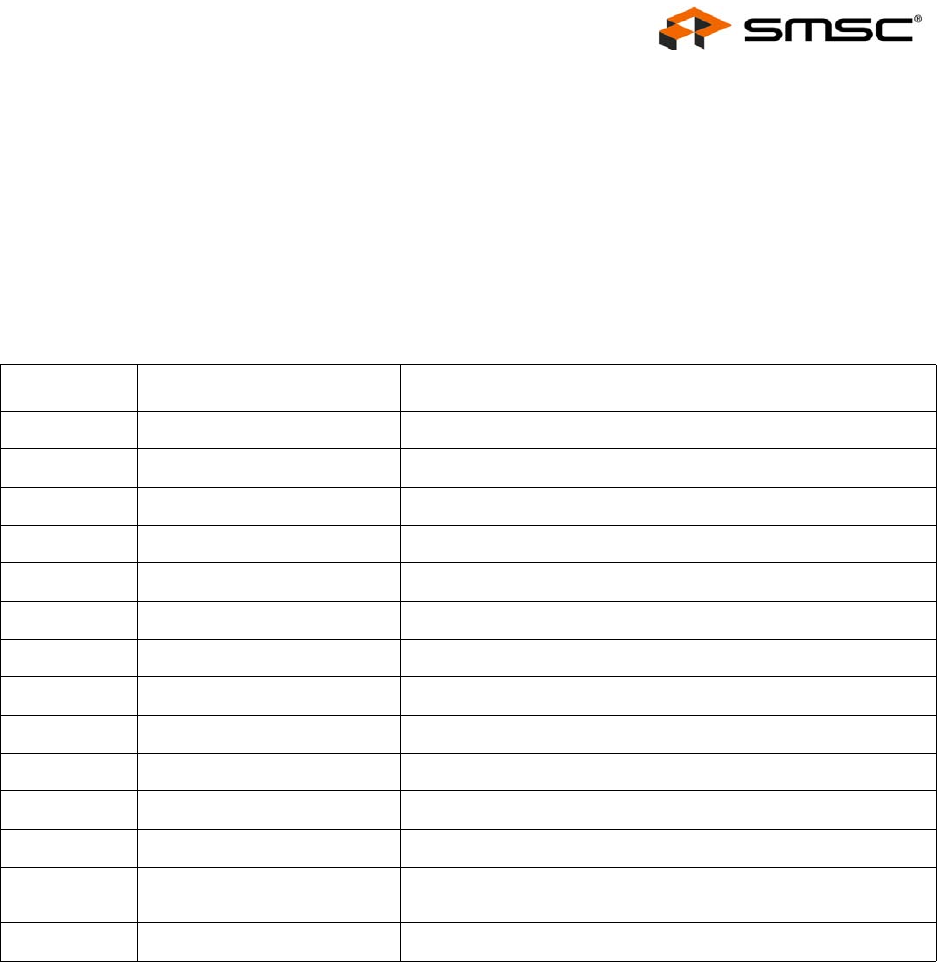

Table 14.6 Host MAC Adressable Registers

INDEX # SYMBOL REGISTER NAME

00h RESERVED Reserved for Future Use

01h HMAC_CR Host MAC Control Register, Section 14.3.1

02h HMAC_ADDRH Host MAC Address High Register, Section 14.3.2

03h HMAC_ADDRL Host MAC Address Low Register, Section 14.3.3

04h HMAC_HASHH Host MAC Multicast Hash Table High Register, Section 14.3.4

05h HMAC_HASHL Host MAC Multicast Hash Table Low Register, Section 14.3.5

06h HMAC_MII_ACC Host MAC MII Access Register, Section 14.3.6

07h HMAC_MII_DATA Host MAC MII Data Register, Section 14.3.7

08h HMAC_FLOW Host MAC Flow Control Register, Section 14.3.8

09h HMAC_VLAN1 Host MAC VLAN1 Tag Register, Section 14.3.9

0Ah HMAC_VLAN2 Host MAC VLAN2 Tag Register, Section 14.3.10

0Bh HMAC_WUFF Host MAC Wake-up Frame Filter Register, Section 14.3.11

0Ch HMAC_WUCSR Host MAC Wake-up Control and Status Register,

Section 14.3.12

0Dh-FFh RESERVED Reserved for Future Use