Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 41 Revision 1.4 (08-19-08)

DATASHEET

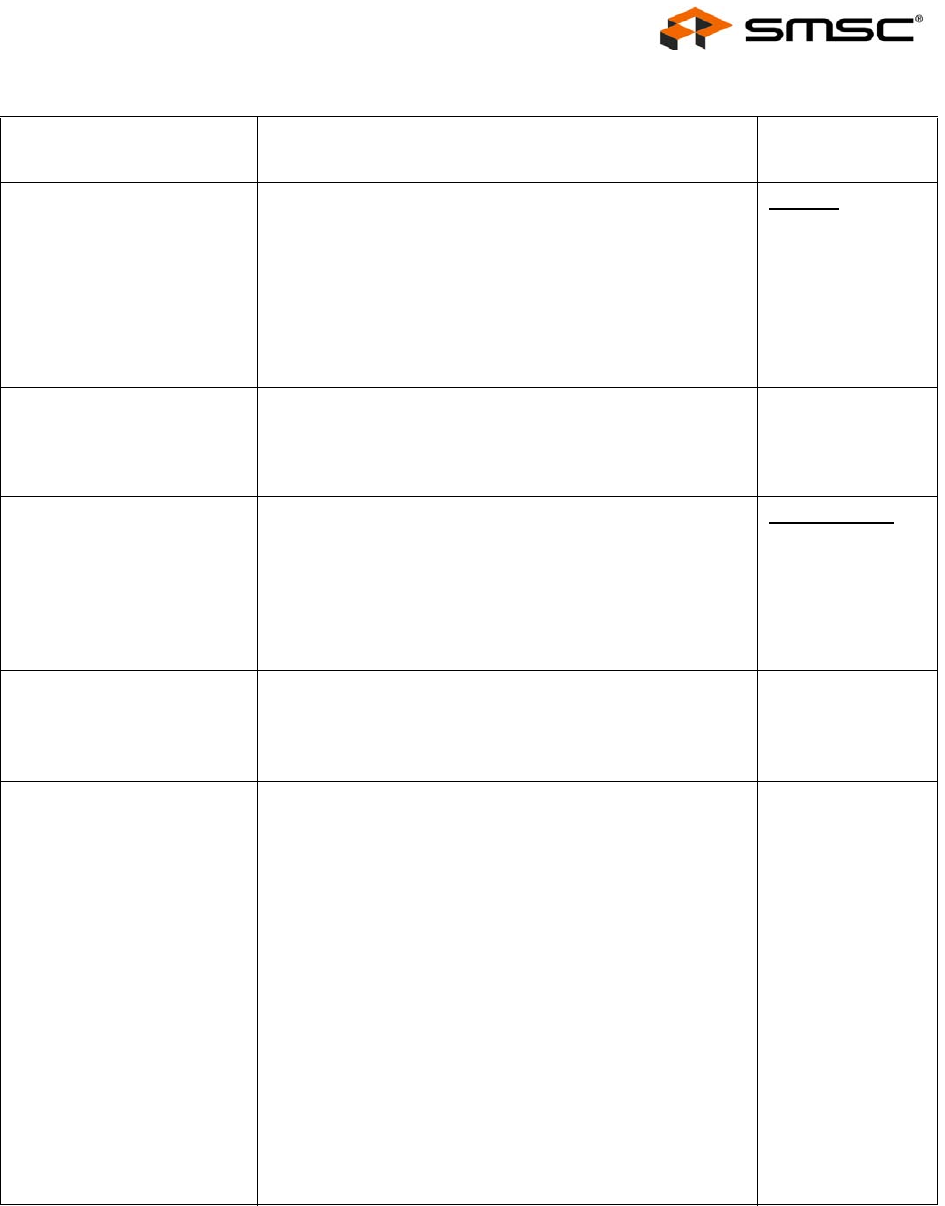

Table 4.2 Soft-Strap Configuration Strap Definitions

STRAP NAME DESCRIPTION

PIN / DEFAULT

VALUE

LED_en_strap[7:0] LED Enable Straps: Configures the default value for the

LED_EN bits in the LED Configuration Register

(LED_CFG). A high value configures the associated

LED/GPIO pin as a LED. A low value configures the

associated LED/GPIO pin as a GPIO.

Note: One pin configures the default for all 8

LED/GPIOs, but 8 separate bits are loaded by the

EEPROM Loader, allowing individual control over

each LED/GPIO.

LED_EN

LED_fun_strap[1:0] LED Function Straps: Configures the default value for the

LED_FUN bits in the LED Configuration Register

(LED_CFG). When configured low, the corresponding bit

will be cleared. When configured high, the corresponding

bit will be set.

00b

auto_mdix_strap_1 Port 1 Auto-MDIX Enable Strap: Configures the default

value for the Auto-MDIX functionality on Port 1 when the

AMDIXCTL bit in the Port x PHY Special Control/Status

Indication Register

(PHY_SPECIAL_CONTROL_STAT_IND_x) is cleared.

When configured low, Auto-MDIX is disabled. When

configured high, Auto-MDIX is enabled.

Note: If AMDIXCTL is set, this strap had no effect.

AUTO_MDIX_1

manual_mdix_strap_1 Port 1 Manual MDIX Strap: Configures MDI(0) or MDIX(1)

for Port 1 when the auto_mdix_strap_1 is low and the

AMDIXCTL bit of the Port x PHY Special Control/Status

Indication Register

(PHY_SPECIAL_CONTROL_STAT_IND_x) is cleared.

0b

autoneg_strap_1 Port 1 Auto Negotiation Enable Strap: Configures the

default value for the Auto-Negotiation (PHY_AN) enable bit

in the PHY_BASIC_CTRL_1 register (See

Section 14.4.2.1). When configured low, auto-negotiation is

disabled. When configured high, auto-negotiation is

enabled.

This strap also affects the default value of the following bits:

PHY_SPEED_SEL_LSB and PHY_DUPLEX bits of the

Port x PHY Basic Control Register

(PHY_BASIC_CONTROL_x)

10BASE-T Full Duplex (bit 6) and 10BASE-T Half Duplex

(bit 5) bits of the Port x PHY Auto-Negotiation

Advertisement Register (PHY_AN_ADV_x)

MODE[2:0] bits of the Port x PHY Special Modes Register

(PHY_SPECIAL_MODES_x)

Refer to the respective register definition sections for

additional information.

1b