Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 262 SMSC LAN9311/LAN9311i

DATASHEET

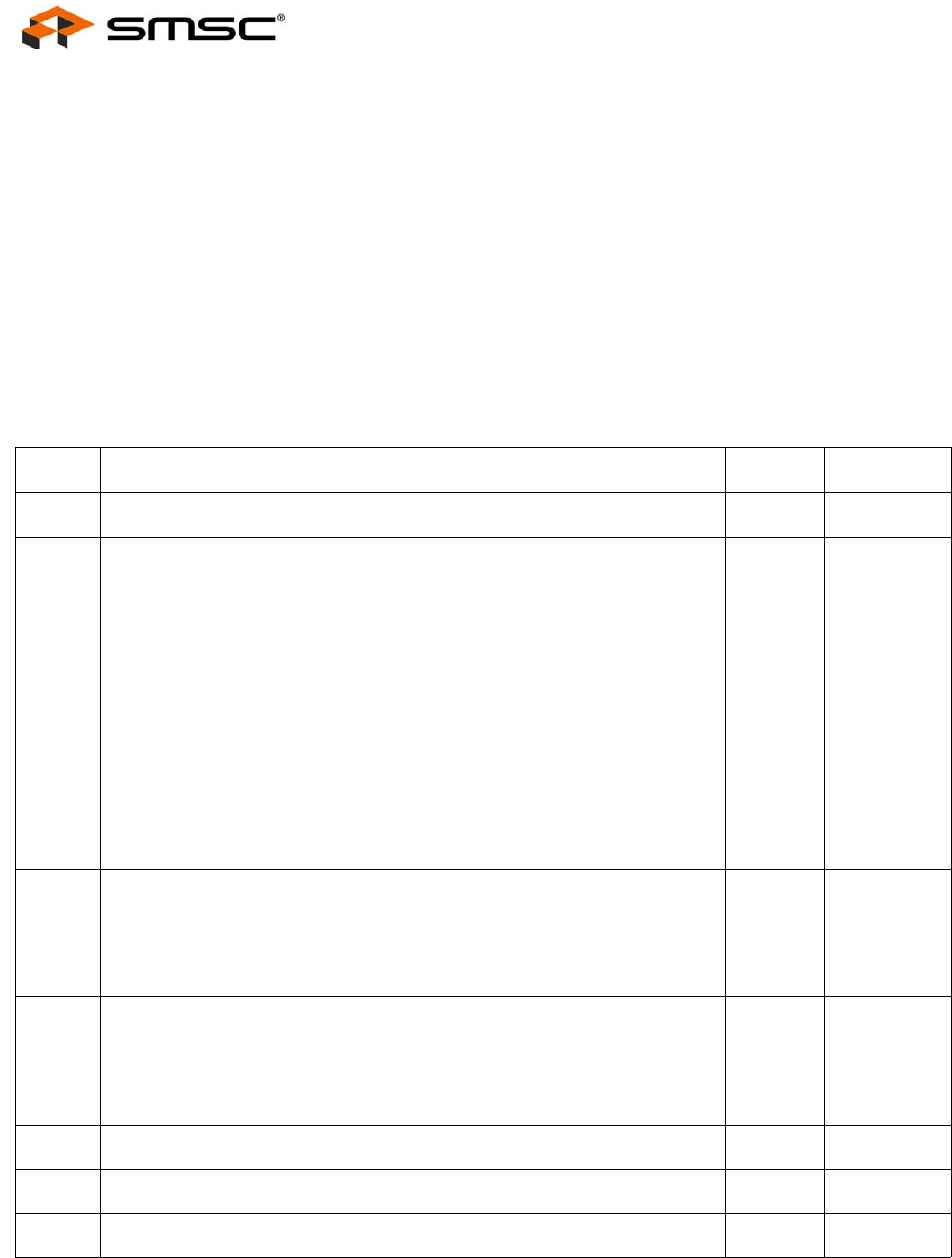

14.2.9.3 Hardware Configuration Register (HW_CFG)

This register allows the configuration of various hardware features including TX/RX FIFO sizes, Host

MAC transmit threshold properties, and software reset. A detailed explanation of the allowable settings

for FIFO memory allocation can be found in Section 9.7.3, "FIFO Memory Allocation Configuration,"

on page 122.

Note: This register can be polled while the LAN9311/LAN9311i is in the reset or not ready state

(READY bit is cleared).

Note: Either half of this register can be read without the need to read the other half.

Offset: 074h Size: 32 bits

BITS DESCRIPTION TYPE DEFAULT

31:28 RESERVED RO -

27 Device Ready (READY)

When set, this bit indicates that the LAN9311/LAN9311i is ready to be

accessed. Upon power-up, nRST reset, soft reset, or digital reset, the host

processor may interrogate this field as an indication that the

LAN9311/LAN9311i has stabilized and is fully active.

This bit can cause an interrupt if enabled.

Note: With the exception of the HW_CFG, PMT_CTRL, BYTE_TEST, and

RESET_CTL registers, read access to any internal resources is

forbidden while the READY bit is cleared. Writes to any address

are invalid until this bit is set.

Note: This bit is identical to bit 0 of the Power Management Control

Register (PMT_CTRL).

RO 0b

26 AMDIX_EN Strap State Port 2

This bit reflects the state of the auto_mdix_strap_2 strap that connects to

the PHY. The strap value is loaded with the level of the auto_mdix_strap_2

during reset and can be re-written by the EEPROM Loader. The strap value

can be overridden by bit 15 and 13 of the Port 2 PHY Special Control/Status

Indication Register (Section 14.4.2.10).

RO Note 14.47

25

AMDIX_EN Strap State Port 1

This bit reflects the state of the auto_mdix_strap_1 strap that connects to

the PHY. The strap value is loaded with the level of the auto_mdix_strap_1

during reset and can be re-written by the EEPROM Loader. The strap value

can be overridden by bit 15 and 13 of the Port 1 PHY Special Control/Status

Indication Register (Section 14.4.2.10).

RO Note 14.48

24:22

RESERVED RO -

21

RESERVED - This bit must be written with 0b for proper operation. R/W 0b

20 Must Be One (MBO). This bit must be set to ‘1’ for normal device operation. R/W 0b