Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 258 SMSC LAN9311/LAN9311i

DATASHEET

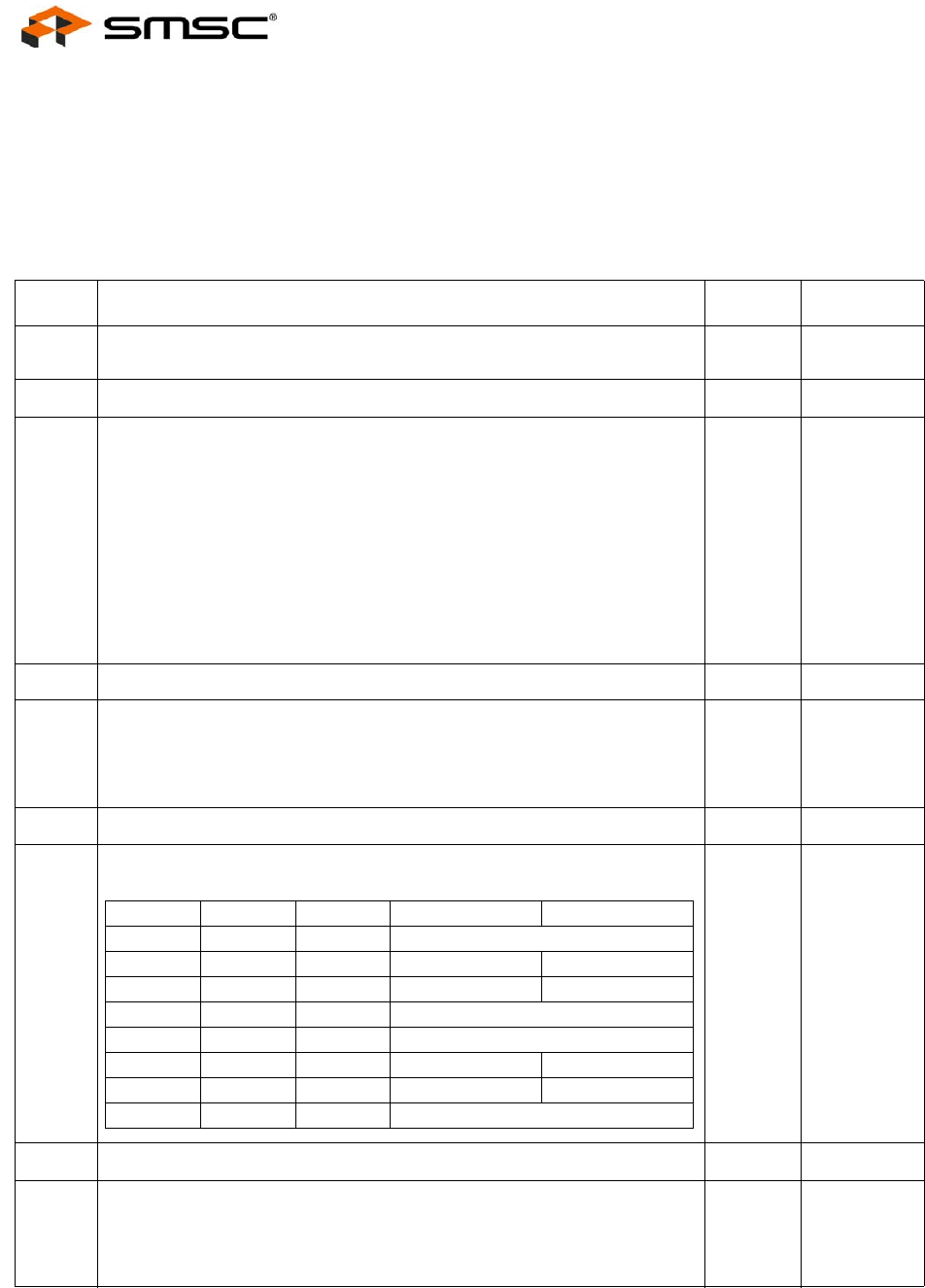

14.2.8.8 Virtual PHY Special Control/Status Register (VPHY_SPECIAL_CONTROL_STATUS)

This read/write register contains a current link speed/duplex indicator and SQE control.

Offset:

Index (decimal):

1DCh

31

Size: 32 bits

BITS DESCRIPTION TYPE DEFAULT

31:16 RESERVED

(See Note 14.42)

RO -

15

RESERVED RO -

14

Switch Looopback MII

When set, transmissions from the switch fabric Port 0(Host MAC) are not

sent to the Host MAC. Instead, they are looped back into the switch engine.

From the MAC viewpoint, this is effectively a FAR LOOPBACK.

If loopback is enabled during half-duplex operation, then the Enable Receive

Own Transmit bit in the Port x MAC Receive Configuration Register

(MAC_RX_CFG_x) must be set for this port. Otherwise, the switch fabric will

ignore receive activity when transmitting in half-duplex mode.

This mode works even if the Isolate bit of the Virtual PHY Basic Control

Register (VPHY_BASIC_CTRL) is set.

R/W 0b

13:8

RESERVED RO -

7

Switch Collision Test MII

When set, the collision signal to the switch fabric Port 0(Host MAC) is active

during transmission from the switch engine.

It is recommended that this bit be used only when using loopback mode.

R/W 0b

6:5

RESERVED RO -

4:2

Current Speed/Duplex Indication

This field indicates the current speed and duplex of the Virtual PHY link.

RO Note 14.43

1

RESERVED RO -

0

SQEOFF

This bit enables/disables the Signal Quality Error (Heartbeat) test.

0: SQE test enabled

1: SQE test disabled

R/W

NASR

Note 14.44

Note 14.45

[4] [3] [2] Speed Duplex

0 0 0 RESERVED

0 0 1 10Mbps half-duplex

0 1 0 100Mbps half-duplex

0 1 1 RESERVED

1 0 0 RESERVED

1 0 1 10Mbps full-duplex

1 1 0 100Mbps full-duplex

1 1 1 RESERVED