Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 50 SMSC LAN9311/LAN9311i

DATASHEET

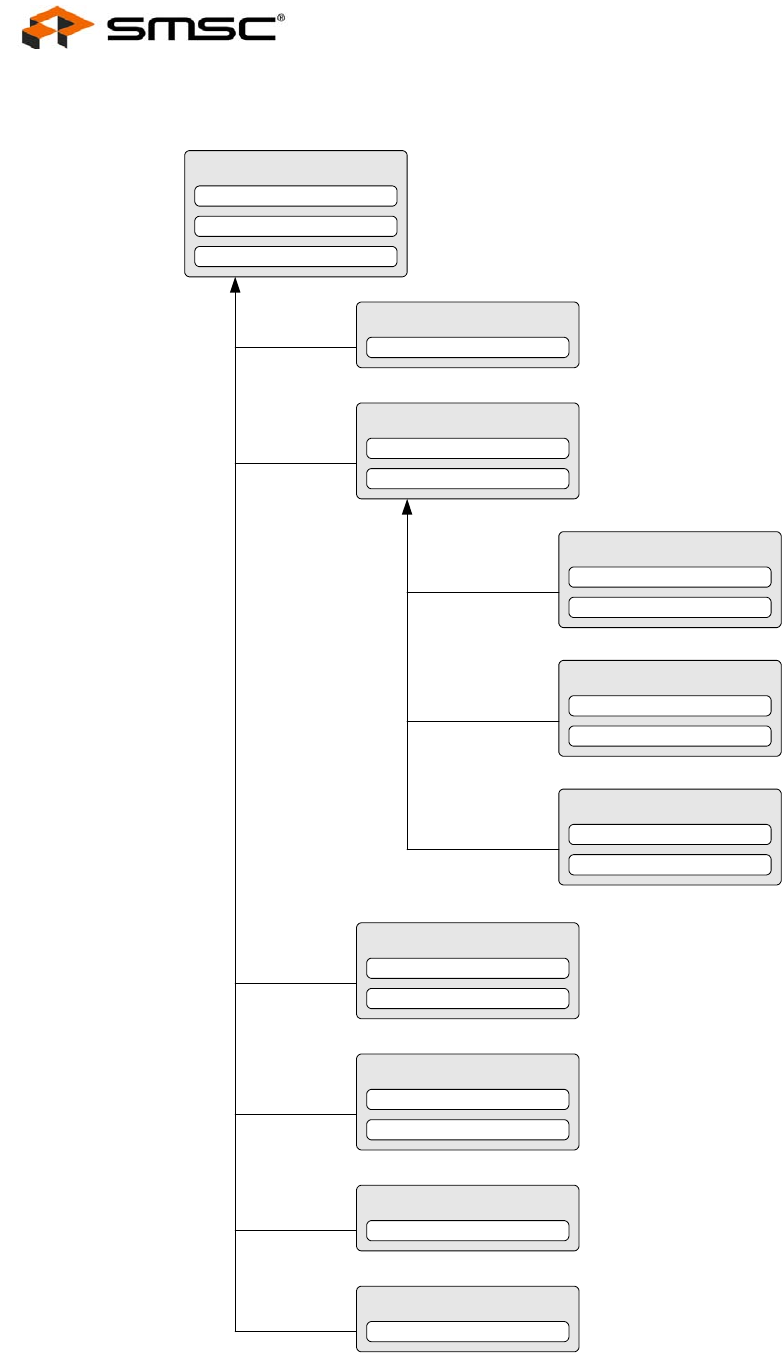

Figure 5.1 Functional Interrupt Register Hierarchy

INT_CFG

INT_STS

INT_EN

Top Level Interrupt Registers

(System CSRs)

1588_INT_STS_EN

1588 Time Stamp Interrupt Register

Bit 29 (1588_EVNT)

of INT_STS register

PHY_INTERRUPT_SOURCE_2

PHY_INTERRUPT_MASK_2

Port 2 PHY Interrupt Registers

Bit 27 (PHY_INT2)

of INT_STS register

PHY_INTERRUPT_SOURCE_1

PHY_INTERRUPT_MASK_1

Port 1 PHY Interrupt Registers

Bit 26 (PHY_INT1)

of INT_STS register

SW_IMR

SW_IPR

Switch Fabric Interrupt Registers

Bit 28 (SWITCH_INT)

of INT_STS register

BM_IMR

BM_IPR

Buffer Manager Interrupt Registers

Bit 6 (BM)

of SW_IPR register

SWE_IMR

SWE_IPR

Switch Engine Interrupt Registers

Bit 5 (SWE)

of SW_IPR register

MAC_IMR_[2,1,MII]

MAC_IPR_[2,1,MII]

Port [2,1,0] MAC Interrupt Registers

Bits [2,1,0] (MAC_[2,1,MII])

of SW_IPR register

PMT_CTRL

Power Management Control Register

Bit 17 (PME_INT)

of INT_STS register

GPIO_INT_STS_EN

GPIO Interrupt Register

Bit 12 (GPIO)

of INT_STS register