Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 446 SMSC LAN9311/LAN9311i

DATASHEET

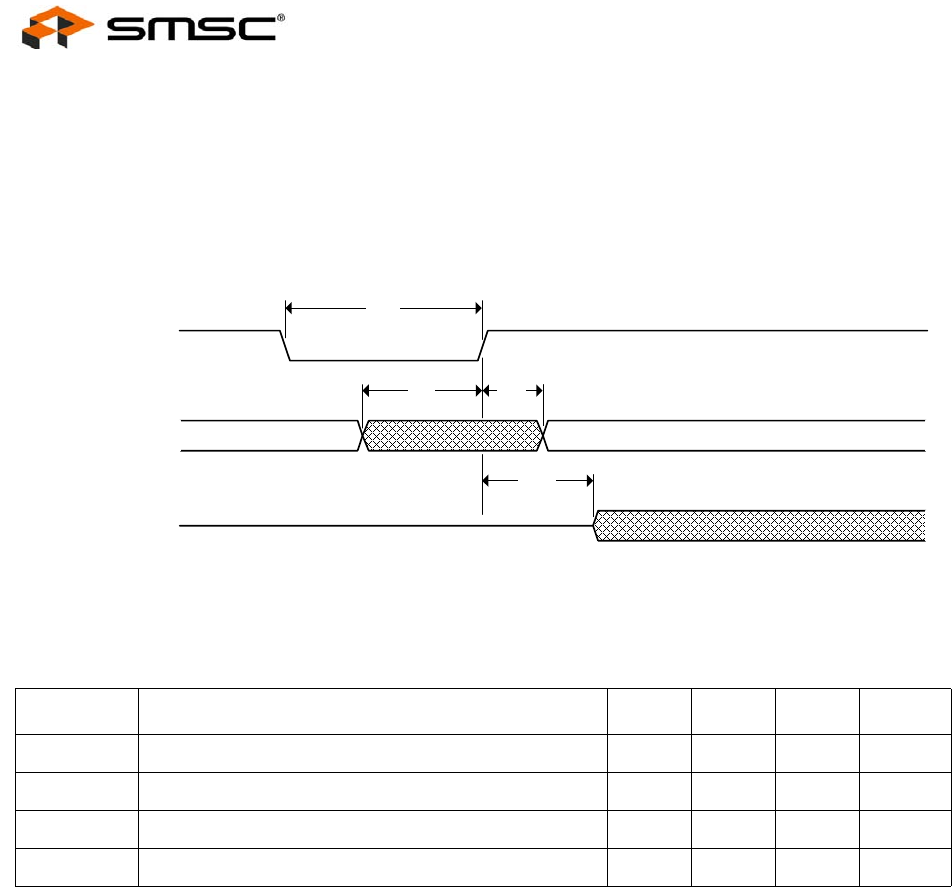

15.5.2 Reset and Configuration Strap Timing

This diagram illustrates the nRST pin timing requirements and its relation to the configuration strap

pins and output drive. Assertion of nRST is not a requirement. However, if used, it must be asserted

for the minimum period specified. Please refer to Section 4.2, "Resets," on page 36 for additional

information.

Note: Device configuration straps are latched as a result of nRST assertion. Refer to Section 4.2.4,

"Configuration Straps," on page 40 for details.

Figure 15.2 nRST Reset Pin Timing

Table 15.6 nRST Reset Pin Timing Values

SYMBOL DESCRIPTION MIN TYP MAX UNITS

t

rstia

nRST input assertion time 200 μS

t

css

Configuration strap pins setup to nRST deassertion 200 nS

t

csh

Configuration strap pins hold after nRST deassertion 10 nS

t

odad

Output drive after deassertion 30 nS

t

css

nRST

Configuration

Strap Pins

t

rstia

t

csh

Output Drive

t

odad