Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 171 Revision 1.4 (08-19-08)

DATASHEET

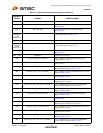

13Ch

1588_SRC_UUID_LO_TX_CAPTURE_2

Port 2 1588 Source UUID Low-DWORD Transmit Capture

Register, Section 14.2.5.8

140h

1588_CLOCK_HI_RX_CAPTURE_MII

Port 0 1588 Clock High-DWORD Receive Capture

Register, Section 14.2.5.1

144h

1588_CLOCK_LO_RX_CAPTURE_MII

Port 0 1588 Clock Low-DWORD Receive Capture Register,

Section 14.2.5.2

148h

1588_SEQ_ID_SRC_UUID_HI_RX_CAPTURE_MII

Port 0 1588 Sequence ID, Source UUID High-WORD

Receive Capture Register, Section 14.2.5.3

14Ch

1588_SRC_UUID_LO_RX_CAPTURE_MII

Port 0 1588 Source UUID Low-DWORD Receive Capture

Register, Section 14.2.5.4

150h

1588_CLOCK_HI_TX_CAPTURE_MII

Port 0 1588 Clock High-DWORD Transmit Capture

Register, Section 14.2.5.5

154h

1588_CLOCK_LO_TX_CAPTURE_MII

Port 0 1588 Clock Low-DWORD Transmit Capture

Register, Section 14.2.5.6

158h

1588_SEQ_ID_SRC_UUID_HI_TX_CAPTURE_MII

Port 0 1588 Sequence ID, Source UUID High-WORD

Transmit Capture Register, Section 14.2.5.7

15Ch

1588_SRC_UUID_LO_TX_CAPTURE_MII

Port 0 1588 Source UUID Low-DWORD Transmit Capture

Register, Section 14.2.5.8

160h

1588_CLOCK_HI_CAPTURE_GPIO_8

GPIO 8 1588 Clock High-DWORD Capture Register,

Section 14.2.5.9

164h

1588_CLOCK_LO_CAPTURE_GPIO_8

GPIO 8 1588 Clock Low-DWORD Capture Register,

Section 14.2.5.10

168h

1588_CLOCK_HI_CAPTURE_GPIO_9

GPIO 9 1588 Clock High-DWORD Capture Register,

Section 14.2.5.11

16Ch

1588_CLOCK_LO_CAPTURE_GPIO_9

GPIO 9 1588 Clock Low-DWORD Capture Register,

Section 14.2.5.12

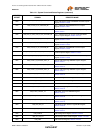

170h

1588_CLOCK_HI

1588 Clock High-DWORD Register, Section 14.2.5.13

174h

1588_CLOCK_LO

1588 Clock Low-DWORD Register, Section 14.2.5.14

178h

1588_CLOCK_ADDEND

1588 Clock Addend Register, Section 14.2.5.15

17Ch

1588_CLOCK_TARGET_HI

1588 Clock Target High-DWORD Register,

Section 14.2.5.16

180h

1588_CLOCK_TARGET_LO

1588 Clock Target Low-DWORD Register,

Section 14.2.5.17

184h

1588_CLOCK_TARGET_RELOAD_HI

1588 Clock Target Reload High-DWORD Register,

Section 14.2.5.18

188h

1588_CLOCK_TARGET_RELOAD_LO

1588 Clock Target Reload/Add Low-DWORD Register,

Section 14.2.5.19

18Ch

1588_AUX_MAC_HI

1588 Auxiliary MAC Address High-WORD Register,

Section 14.2.5.20

190h

1588_AUX_MAC_LO

1588 Auxiliary MAC Address Low-DWORD Register,

Section 14.2.5.21

194h

1588_CONFIG

1588 Configuration Register, Section 14.2.5.22

198h

1588_INT_STS_EN

1588 Interrupt Status Enable Register, Section 14.2.5.23

19Ch

1588_CMD

1588 Command Register, Section 14.2.5.24

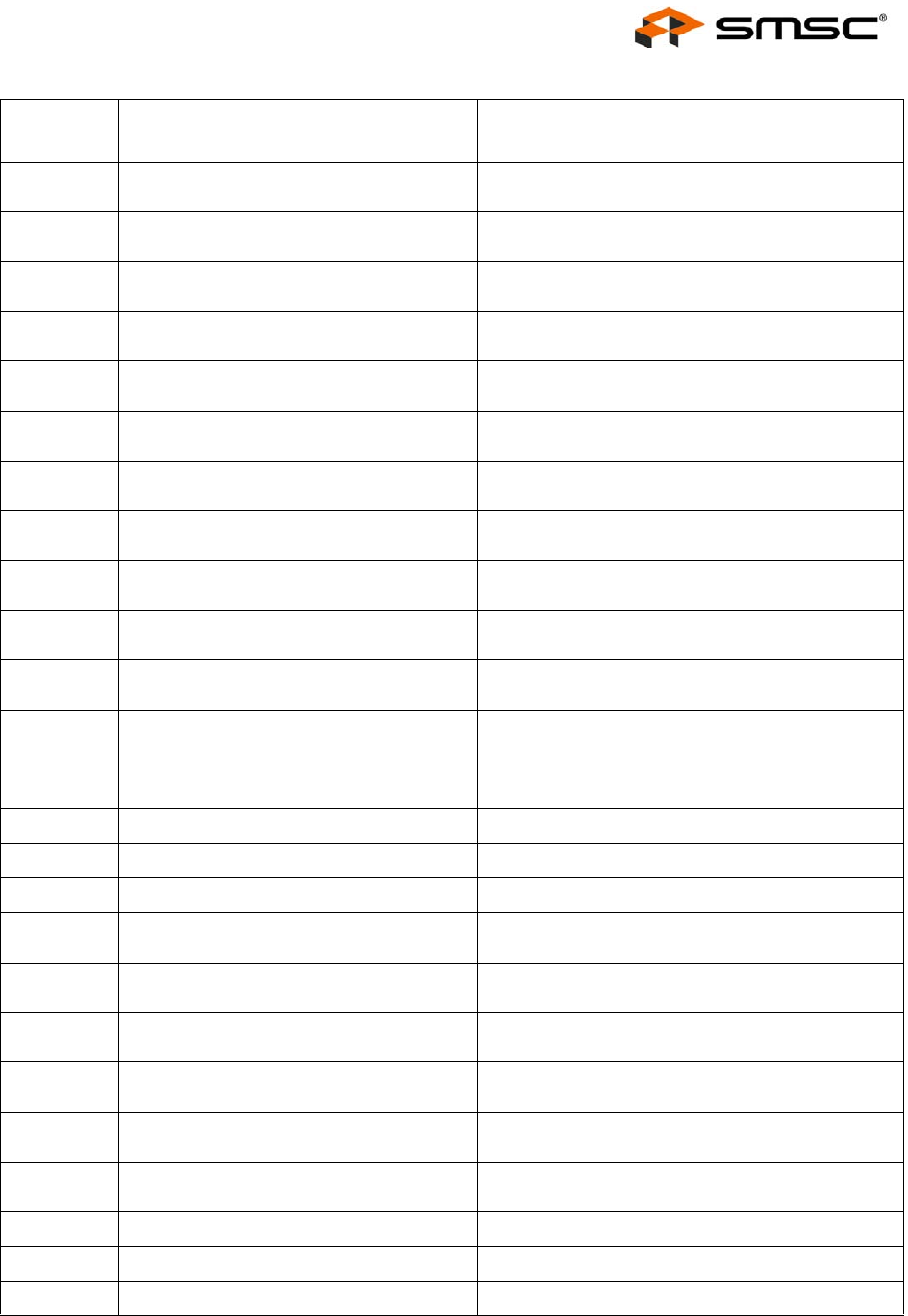

Table 14.1 System Control and Status Registers (continued)

ADDRESS

OFFSET SYMBOL REGISTER NAME