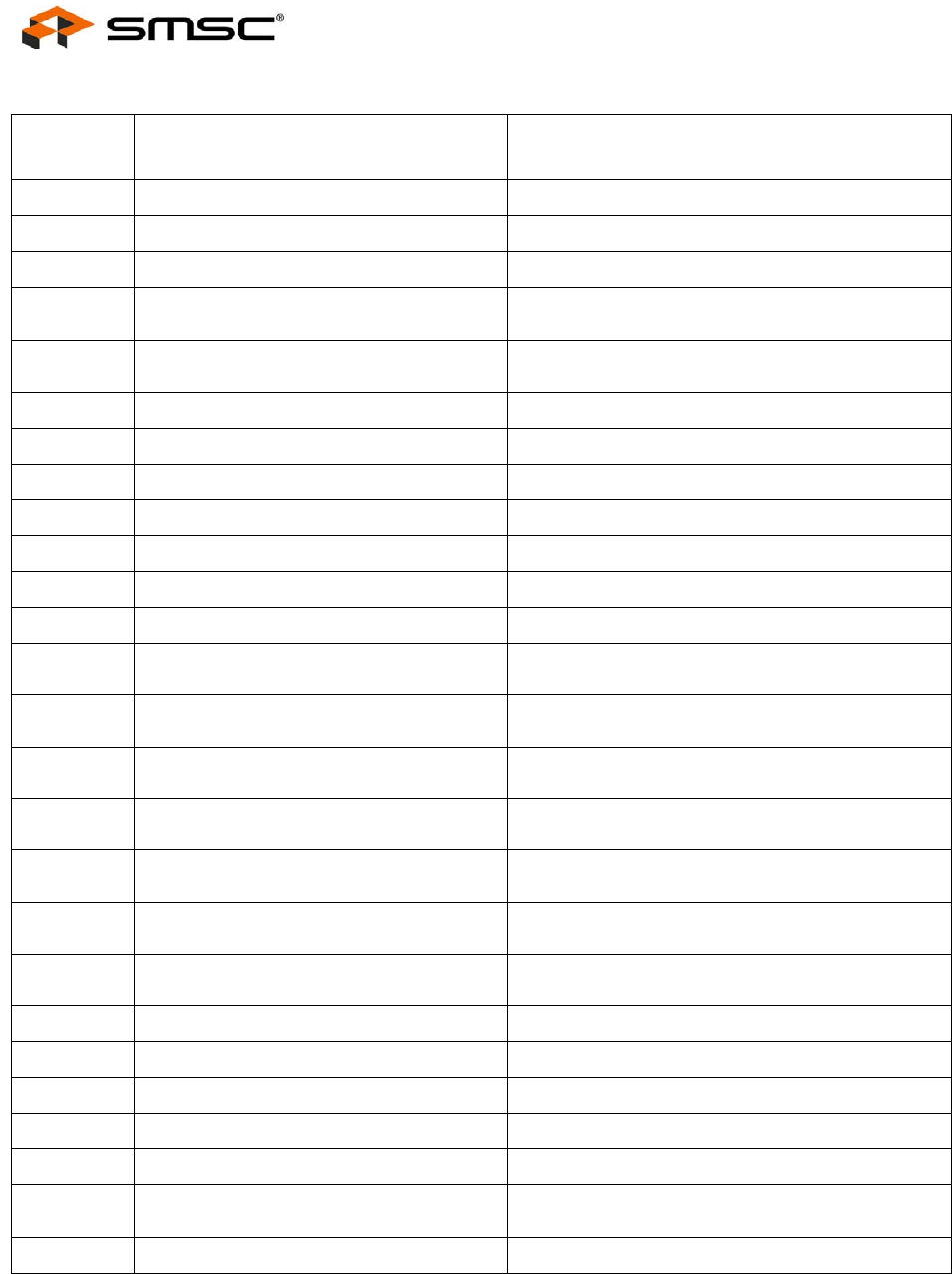

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 172 SMSC LAN9311/LAN9311i

DATASHEET

1A0h

MANUAL_FC_1

Port 1 Manual Flow Control Register, Section 14.2.6.1

1A4h

MANUAL_FC_2

Port 2 Manual Flow Control Register, Section 14.2.6.2

1A8h

MANUAL_FC_MII

Port 0 Flow Control Register, Section 14.2.6.3

1ACh

SWITCH_CSR_DATA

Switch Fabric CSR Interface Data Register,

Section 14.2.6.4

1B0h

SWITCH_CSR_CMD

Switch Fabric CSR Interface Command Register,

Section 14.2.6.5

1B4h

E2P_CMD

EEPROM Command Register, Section 14.2.4.1

1B8h

E2P_DATA

EEPROM Data Register, Section 14.2.4.2

1BCh

LED_CFG

LED Configuration Register, Section 14.2.3.4

1C0h

VPHY_BASIC_CTRL

Virtual PHY Basic Control Register, Section 14.2.8.1

1C4h

VPHY_BASIC_STATUS

Virtual PHY Basic Status Register, Section 14.2.8.2

1C8h

VPHY_ID_MSB

Virtual PHY Identification MSB Register, Section 14.2.8.3

1CCh

VPHY_ID_LSB

Virtual PHY Identification LSB Register, Section 14.2.8.4

1D0h

VPHY_AN_ADV

Virtual PHY Auto-Negotiation Advertisement Register,

Section 14.2.8.5

1D4h

VPHY_AN_LP_BASE_ABILITY

Virtual PHY Auto-Negotiation Link Partner Base Page

Ability Register, Section 14.2.8.6

1D8h

VPHY_AN_EXP

Virtual PHY Auto-Negotiation Expansion Register,

Section 14.2.8.7

1DCh

VPHY_SPECIAL_CONTROL_STATUS

Virtual PHY Special Control/Status Register,

Section 14.2.8.8

1E0h

GPIO_CFG

General Purpose I/O Configuration Register,

Section 14.2.3.1

1E4h

GPIO_DATA_DIR

General Purpose I/O Data & Direction Register,

Section 14.2.3.2

1E8h

GPIO_INT_STS_EN

General Purpose I/O Interrupt Status and Enable Register,

Section 14.2.3.3

1ECh

RESERVED

Reserved for Future Use

1F0h

SWITCH_MAC_ADDRH

Switch MAC Address High Register, Section 14.2.6.6

1F4h

SWITCH_MAC_ADDRL

Switch MAC Address Low Register, Section 14.2.6.7

1F8h

RESET_CTL

Reset Control Register, Section 14.2.9.8

1FCh

RESERVED

Reserved for Future Use

200h-2DCh

SWITCH_CSR_DIRECT_DATA

Switch Engine CSR Interface Direct Data Register,

Section 14.2.6.8

2E0h-3FFh

RESERVED

Reserved for Future Use

Table 14.1 System Control and Status Registers (continued)

ADDRESS

OFFSET SYMBOL REGISTER NAME