Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 368 SMSC LAN9311/LAN9311i

DATASHEET

14.5.3 Switch Engine CSRs

This section details the switch engine related CSRs. These registers allow configuration and monitoring

of the various switch engine components including the ALR, VLAN, Port VID, and DIFFSERV tables.

A list of the general switch CSRs and their corresponding register numbers is included in Table 14.12.

14.5.3.1 Switch Engine ALR Command Register (SWE_ALR_CMD)

This register is used to manually read and write MAC addresses from/into the ALR table.

For a read access, the Switch Engine ALR Read Data 0 Register (SWE_ALR_RD_DAT_0) and Switch

Engine ALR Read Data 1 Register (SWE_ALR_RD_DAT_1) should be read following the setting of bit

1(Get First Entry) or bit 0(Get Next Entry) of this register.

For write access, the Switch Engine ALR Write Data 0 Register (SWE_ALR_WR_DAT_0) and Switch

Engine ALR Write Data 1 Register (SWE_ALR_WR_DAT_1) registers should first be written with the

MAC address, followed by the setting of bit 2(Make Entry) of this register. The Make Pending bit in the

Switch Engine ALR Command Status Register (SWE_ALR_CMD_STS) register indicates when the

command is finished.

Refer to Chapter 6, "Switch Fabric," on page 55 for more information.

Register #: 1800h Size: 32 bits

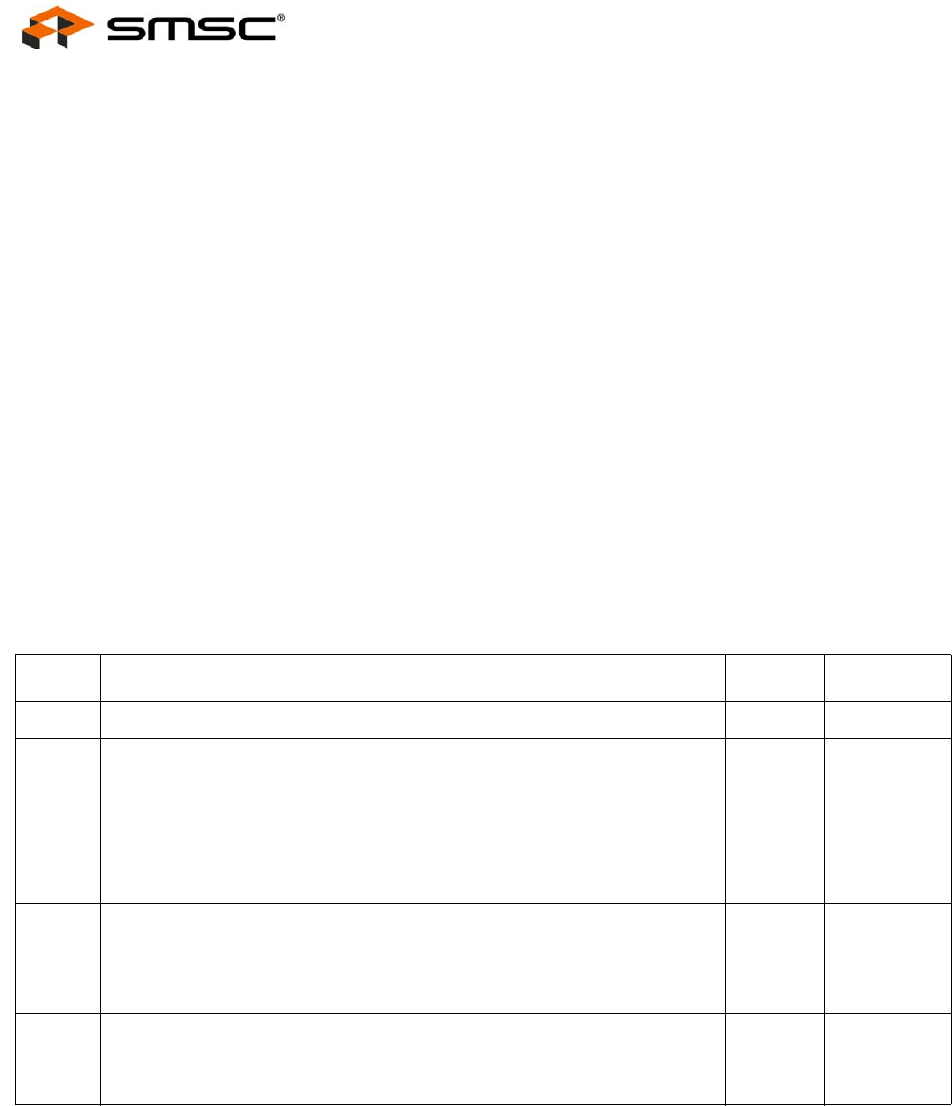

BITS DESCRIPTION TYPE DEFAULT

31:3 RESERVED RO -

2

Make Entry

When set, the contents of ALR_WR_DAT_0 and ALR_WR_DAT_1 are

written into the ALR table. The ALR logic determines the location where the

entry is written. This command can also be used to change or delete a

previously written or automatically learned entry. This bit has no affect when

written low. This bit must be cleared once the ALR Make command is

completed, which can be determined by the ALR Status bit in the Switch

Engine ALR Command Status Register (SWE_ALR_CMD_STS) register.

R/W 0b

1

Get First Entry

When set, the ALR read pointer is reset to the beginning of the ALR table

and the ALR table is searched for the first valid entry, which is loaded into

the ALR_RD_DAT_0 and ALR_RD_DAT_1 registers. The bit has no affect

when written low. This bit must be cleared after it is set.

R/W 0b

0

Get Next Entry

When set, the next valid entry in the ALR MAC address table is loaded into

the ALR_RD_DAT_0 and ALR_RD_DAT_1 registers. This bit has no affect

when written low. This bit must be cleared after it is set.

R/W 0b