Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 449 Revision 1.4 (08-19-08)

DATASHEET

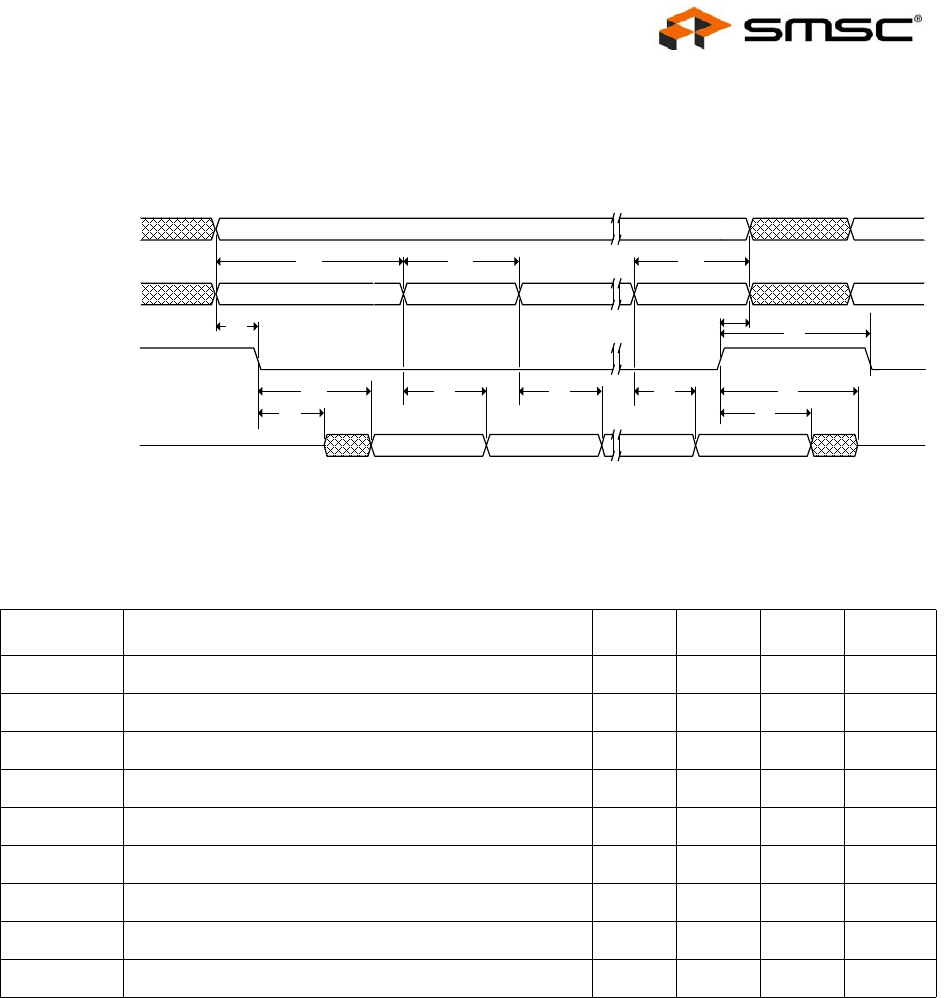

15.5.5 PIO Burst Read Cycle Timing

Please refer to Section 8.5.5, "PIO Burst Reads," on page 108 for a functional description of this mode.

Note: A host PIO burst read cycle begins when both nCS and nRD are asserted. The cycle ends

when either or both nCS and nRD are de-asserted. These signals may be asserted and de-

asserted in any order.

Note: A[1] must toggle, fresh data is supplied each time A[1] toggles.

Figure 15.5 PIO Burst Read Cycle Timing

Table 15.9 PIO Burst Read Cycle Timing Values

SYMBOL DESCRIPTION MIN TYP MAX UNITS

t

csh

nCS, nRD De-assertion Time 13 nS

t

csdv

nCS, nRD Valid to Data Valid 30 nS

t

acyc

Address Cycle Time 45 nS

t

asu

Address Setup to nCS, nRD Valid 0 nS

t

adv

Address Stable to Data Valid 40 nS

t

ah

Address Hold Time 0 nS

t

don

Data Buffer Turn On Time 0 nS

t

doff

Data Buffer Turn Off Time 9 nS

t

doh

Data Output Hold Time 0 nS

A[4:1]

nCS, nRD

D[15:0]

A[x:5], END_SEL

t

asu

t

acyc

t

acyc

t

acyc

t

ah

t

csh

t

adv

t

adv

t

adv

t

csdv

t

don

t

doh

t

doff