Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 306 SMSC LAN9311/LAN9311i

DATASHEET

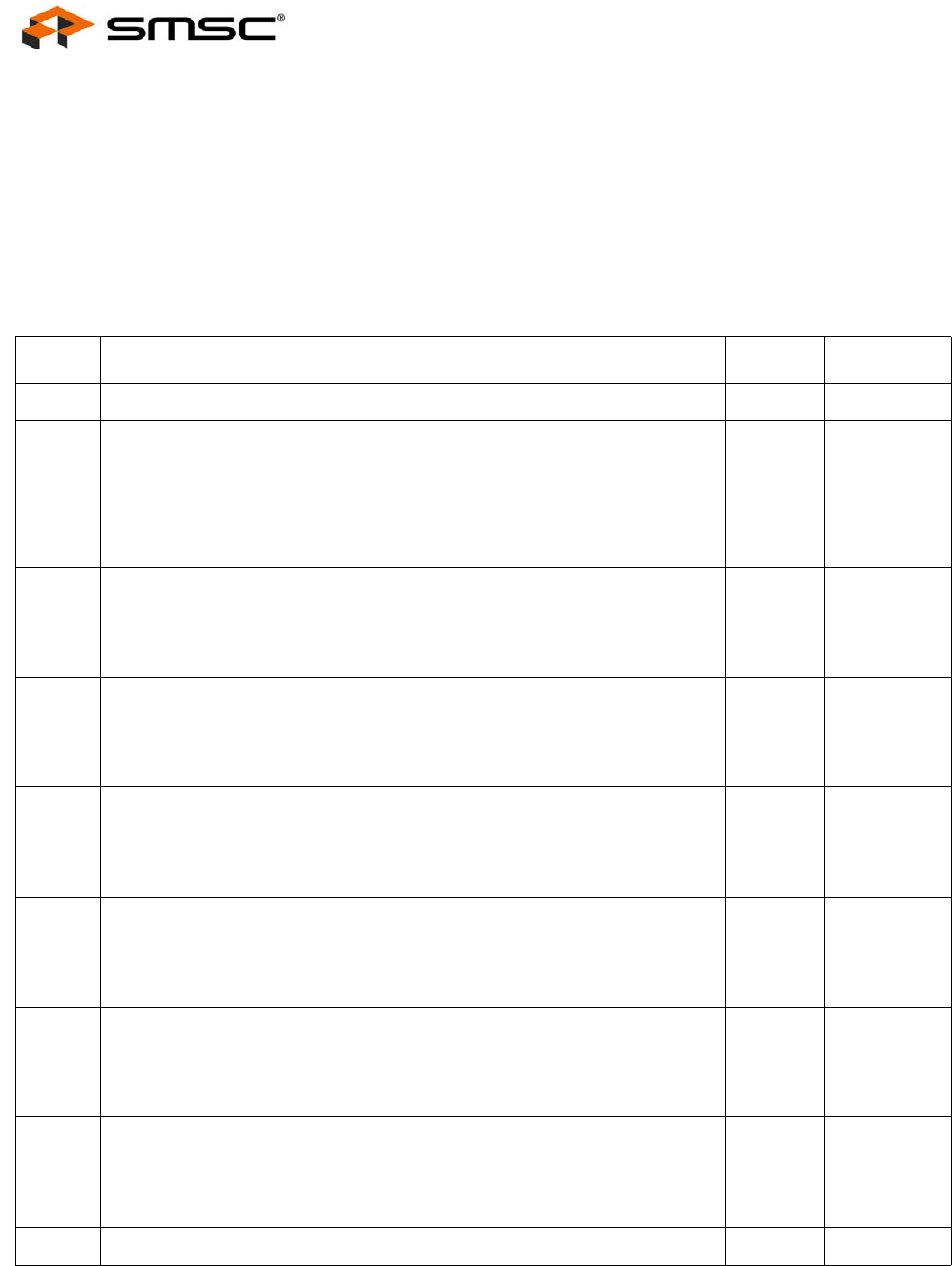

14.4.2.11 Port x PHY Interrupt Source Flags Register (PHY_INTERRUPT_SOURCE_x)

This read-only register is used to determine to source of various Port x PHY interrupts. All interrupt

source bits in this register are read-only and latch high upon detection of the corresponding interrupt

(if enabled). A read of this register clears the interrupts. These interrupts are enabled or masked via

the Port x PHY Interrupt Mask Register (PHY_INTERRUPT_MASK_x).

Index (decimal): 29 Size: 16 bits

BITS DESCRIPTION TYPE DEFAULT

15:8 RESERVED RO -

7

INT7

This interrupt source bit indicates when the ENERGYON bit of the Port x

PHY Mode Control/Status Register (PHY_MODE_CONTROL_STATUS_x)

has been set.

0: Not source of interrupt

1: ENERGYON generated

RO/LH 0b

6

INT6

This interrupt source bit indicates Auto-Negotiation is complete.

0: Not source of interrupt

1: Auto-Negotiation complete

RO/LH 0b

5

INT5

This interrupt source bit indicates a remote fault has been detected.

0: Not source of interrupt

1: Remote fault detected

RO/LH 0b

4

INT4

This interrupt source bit indicates a Link Down (link status negated).

0: Not source of interrupt

1: Link Down (link status negated)

RO/LH 0b

3

INT3

This interrupt source bit indicates an Auto-Negotiation LP acknowledge.

0: Not source of interrupt

1: Auto-Negotiation LP acknowledge

RO/LH 0b

2

INT2

This interrupt source bit indicates a Parallel Detection fault.

0: Not source of interrupt

1: Parallel Detection fault

RO/LH 0b

1

INT1

This interrupt source bit indicates an Auto-Negotiation page received.

0: Not source of interrupt

1: Auto-Negotiation page received

RO/LH 0b

0

RESERVED RO -