Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 275 Revision 1.4 (08-19-08)

DATASHEET

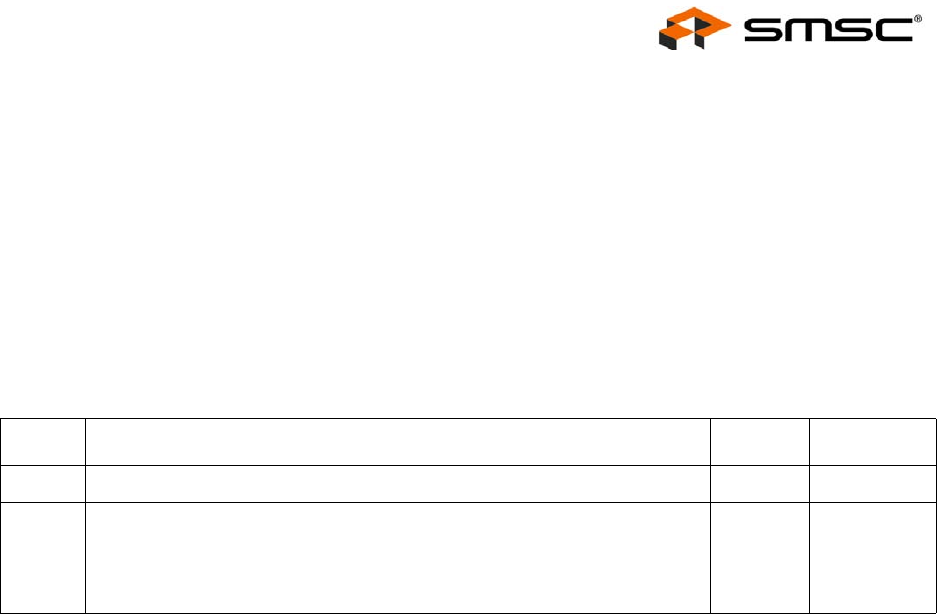

14.3.2 Host MAC Address High Register (HMAC_ADDRH)

This read/write register contains the upper 16-bits of the physical address of the Host MAC. The

contents of this register are optionally loaded from the EEPROM at power-on through the EEPROM

Loader if a programmed EEPROM is detected. The least significant byte of this register (bits [7:0]) is

loaded from address 05h of the EEPROM. The second byte (bits [15:8]) is loaded from address 06h

of the EEPROM. Section 9.6, "Host MAC Address," on page 120 details the byte ordering of the

HMAC_ADDRL and HMAC_ADDRH registers with respect to the reception of the Ethernet physical

address. Please refer to Section 10.2, "I2C/Microwire Master EEPROM Controller," on page 138 for

more information on the EEPROM Loader.

Offset: 2h Size: 32 bits

BITS DESCRIPTION TYPE DEFAULT

31:16 RESERVED RO -

15:0

Physical Address [47:32]

This field contains the upper 16-bits (47:32) of the Physical Address of the

Host MAC. The content of this field is undefined until loaded from the

EEPROM at power-on. The host can update the contents of this field after

the initialization process has completed.

R/W FFFFh