Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 270 SMSC LAN9311/LAN9311i

DATASHEET

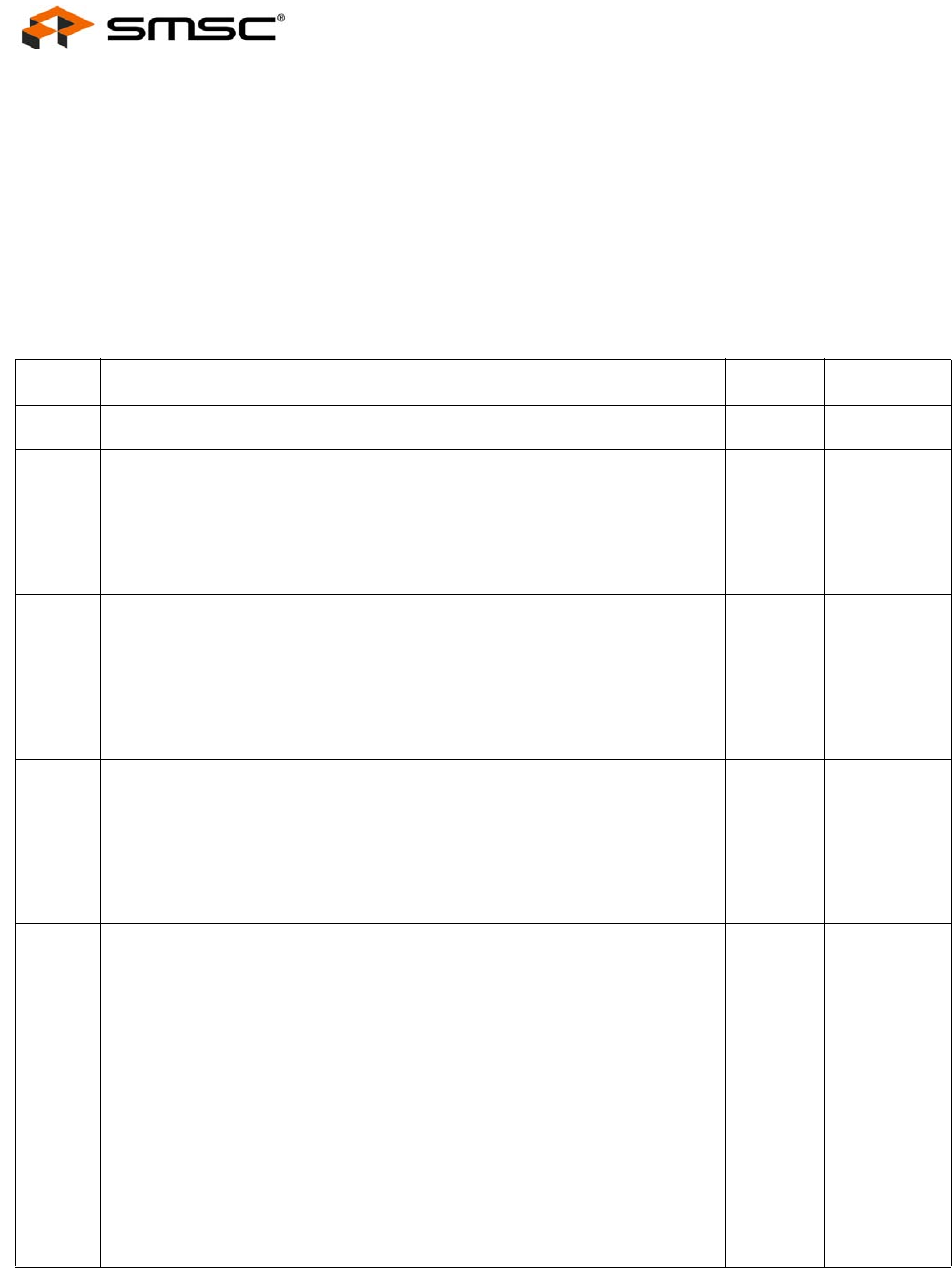

14.2.9.8 Reset Control Register (RESET_CTL)

This register contains software controlled resets.

Note: This register can be read while the LAN9311/LAN9311i is in the reset or not ready states.

Note: Either half of this register can be read without the need to read the other half.

Offset: 1F8h Size: 32 bits

BITS DESCRIPTION TYPE DEFAULT

31:4 RESERVED RO -

3 Virtual PHY Reset (VPHY_RST)

Setting this bit resets the Virtual PHY. When the Virtual PHY is released from

reset, this bit is automatically cleared. All writes to this bit are ignored while

this bit is set.

Note: This bit is not accessible via the EEPROM Loader.

R/W

SC

0b

2

Port 2 PHY Reset (PHY2_RST)

Setting this bit resets the Port 2 PHY. The internal logic automatically holds

the PHY reset for a minimum of 102uS. When the Port 2 PHY is released

from reset, this bit is automatically cleared. All writes to this bit are ignored

while this bit is set.

Note: This bit is not accessible via the EEPROM Loader.

R/W

SC

0b

1

Port 1 PHY Reset (PHY1_RST)

Setting this bit resets the Port 1 PHY. The internal logic automatically holds

the PHY reset for a minimum of 102uS. When the Port 1 PHY is released

from reset, this bit is automatically cleared. All writes to this bit are ignored

while this bit is set.

Note: This bit is not accessible via the EEPROM Loader.

R/W

SC

0b

0

Digital Reset (DIGITAL_RST)

Setting this bit resets the complete chip except the PLL, Virtual PHY, Port 1

PHY, and Port 2 PHY. The EEPROM Loader will automatically reload the

configuration following this reset, but will not reset the Virtual PHY, Port 1

PHY, or Port 2 PHY. If desired, the above PHY resets can be issued once

the device is configured. All system CSRs are reset except for any NASR

type bits. Any in progress EEPROM commands (including RELOAD) are

terminated.

When the chip is released from reset, this bit is automatically cleared. This

bit should be polled to determine when the reset is complete. All writes to

this bit are ignored while this bit is set.

Note: The LAN9311/LAN9311imust always be read at least once after

power-up or reset to ensure that write operations function properly.

Note: This bit is not accessible via the EEPROM Loader.

R/W

SC

0b