Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 317 Revision 1.4 (08-19-08)

DATASHEET

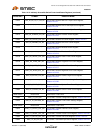

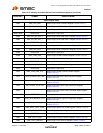

1847h

SWE_INGRESS_PORT_TYP

Switch Engine Ingress Port Type Register, Section 14.5.3.22

1848h SWE_BCST_THROT Switch Engine Broadcast Throttling Register, Section 14.5.3.23

1849h SWE_ADMT_N_MEMBER Switch Engine Admit Non Member Register, Section 14.5.3.24

184Ah

SWE_INGRESS_RATE_CFG

Switch Engine Ingress Rate Configuration Register,

Section 14.5.3.25

184Bh

SWE_INGRESS_RATE_CMD

Switch Engine Ingress Rate Command Register,

Section 14.5.3.26

184Ch

SWE_INGRESS_RATE_CMD_STS

Switch Engine Ingress Rate Command Status Register,

Section 14.5.3.27

184Dh

SWE_INGRESS_RATE_WR_DATA

Switch Engine Ingress Rate Write Data Register,

Section 14.5.3.28

184Eh

SWE_INGRESS_RATE_RD_DATA

Switch Engine Ingress Rate Read Data Register,

Section 14.5.3.29

184Fh RESERVED Reserved for Future Use

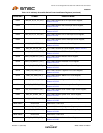

1850h SWE_FILTERED_CNT_MII Switch Engine Port 0 Ingress Filtered Count Register,

Section 14.5.3.30

1851h SWE_FILTERED_CNT_1 Switch Engine Port 1 Ingress Filtered Count Register,

Section 14.5.3.31

1852h SWE_FILTERED_CNT_2 Switch Engine Port 2 Ingress Filtered Count Register,

Section 14.5.3.32

1853h-1854h RESERVED Reserved for Future Use

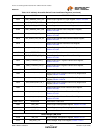

1855h

SWE_INGRESS_REGEN_TBL_MII

Switch Engine Port 0 Ingress VLAN Priority Regeneration

Register, Section 14.5.3.33

1856h

SWE_INGRESS_REGEN_TBL_1

Switch Engine Port 1 Ingress VLAN Priority Regeneration

Register, Section 14.5.3.34

1857h

SWE_INGRESS_REGEN_TBL_2

Switch Engine Port 2 Ingress VLAN Priority Regeneration

Register, Section 14.5.3.35

1858h

SWE_LRN_DISCRD_CNT_MII

Switch Engine Port 0 Learn Discard Count Register,

Section 14.5.3.36

1859h

SWE_LRN_DISCRD_CNT_1

Switch Engine Port 1 Learn Discard Count Register,

Section 14.5.3.37

185Ah

SWE_LRN_DISCRD_CNT_2

Switch Engine Port 2 Learn Discard Count Register,

Section 14.5.3.38

185Bh-187Fh RESERVED Reserved for Future Use

1880h SWE_IMR Switch Engine Interrupt Mask Register, Section 14.5.3.39

1881h SWE_IPR Switch Engine Interrupt Pending Register, Section 14.5.3.40

1882h-1BFFh RESERVED Reserved for Future Use

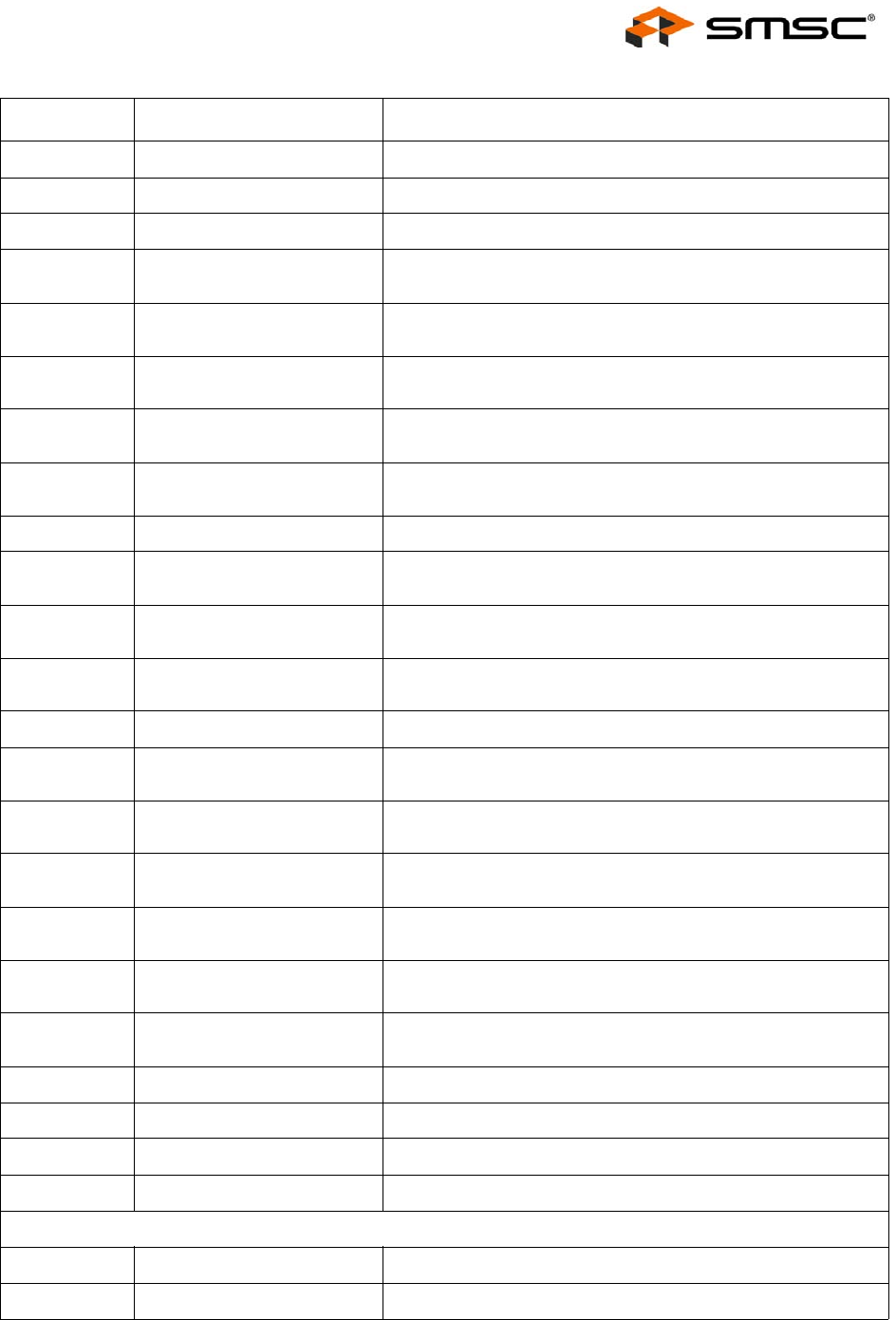

Buffer Manager (BM) CSRs

1C00h BM_CFG Buffer Manager Configuration Register, Section 14.5.4.1

1C01h BM_DROP_LVL Buffer Manager Drop Level Register, Section 14.5.4.2

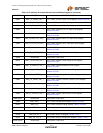

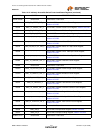

Table 14.12 Indirectly Accessible Switch Control and Status Registers (continued)

REGISTER # SYMBOL REGISTER NAME