Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 152 SMSC LAN9311/LAN9311i

DATASHEET

10.2.4.2 EEPROM Valid Flag

Following the release of nRST, POR, DIGITAL_RST, or a RELOAD command, the EEPROM Loader

starts by reading the first byte of data from the EEPROM. If the value of A5h is not read from the first

byte, the EEPROM Loader will load the current configuration strap values into the PHY registers (see

Section 10.2.4.4.1) and then terminate, clearing the EPC_BUSY bit in the EEPROM Command

Register (E2P_CMD). Otherwise, the EEPROM Loader will continue reading sequential bytes from the

EEPROM.

10.2.4.3 MAC Address

The next six bytes in the EEPROM, after the EEPROM Valid Flag, are written into the Host MAC

Address High Register (HMAC_ADDRH) and Host MAC Address Low Register (HMAC_ADDRL), and

the Switch Fabric MAC Address High Register (SWITCH_MAC_ADDRH) and Switch Fabric MAC

Address Low Register (SWITCH_MAC_ADDRL). The EEPROM bytes are written into the MAC

address registers in the order specified in Table 10.7. Refer to Section 9.6, "Host MAC Address," on

page 120 for additional information on MAC address loading.

10.2.4.3.1 HOST MAC ADDRESS RELOAD

While the EEPROM Loader is in the wait state, if a Host MAC reset is detected (via the Soft Reset bit

in the Hardware Configuration Register (HW_CFG)), the EEPROM Loader will read byte 0. If the byte

0 value is A5h, the EEPROM Loader will read bytes 1 through 6 from the EEPROM and reload the

Host MAC Address High Register (HMAC_ADDRH) and Host MAC Address Low Register

(HMAC_ADDRL). During this time, the EPC_BUSY bit in the EEPROM Command Register

(E2P_CMD) is set.

Note: The switch MAC address registers are not reloaded due to this condition.

10.2.4.4 Soft-Straps

The 7

th

byte of data to be read from the EEPROM is the Configuration Strap Values Valid Flag. If this

byte has a value of A5h, the next 4 bytes of data (8-11) are written into the configuration strap registers

per the assignments detailed in Table 10.8. If the flag byte is not A5h, these next 4 bytes are skipped

(they are still read to maintain the data burst, but are discarded). However, the current configuration

strap values are still loaded into the PHY registers (see Section 10.2.4.4.1). Refer to Section 4.2.4,

"Configuration Straps," on page 40 for more information on the LAN9311/LAN9311i configuration

straps.

10.2.4.4.1 PHY REGISTERS SYNCHRONIZATION

Some PHY register defaults are based on configuration straps. In order to maintain consistency

between the updated configuration strap registers and the PHY registers, the Port x PHY Auto-

Negotiation Advertisement Register (PHY_AN_ADV_x), Port x PHY Special Modes Register

(PHY_SPECIAL_MODES_x), and Port x PHY Basic Control Register (PHY_BASIC_CONTROL_x) are

written when the EEPROM Loader is run.

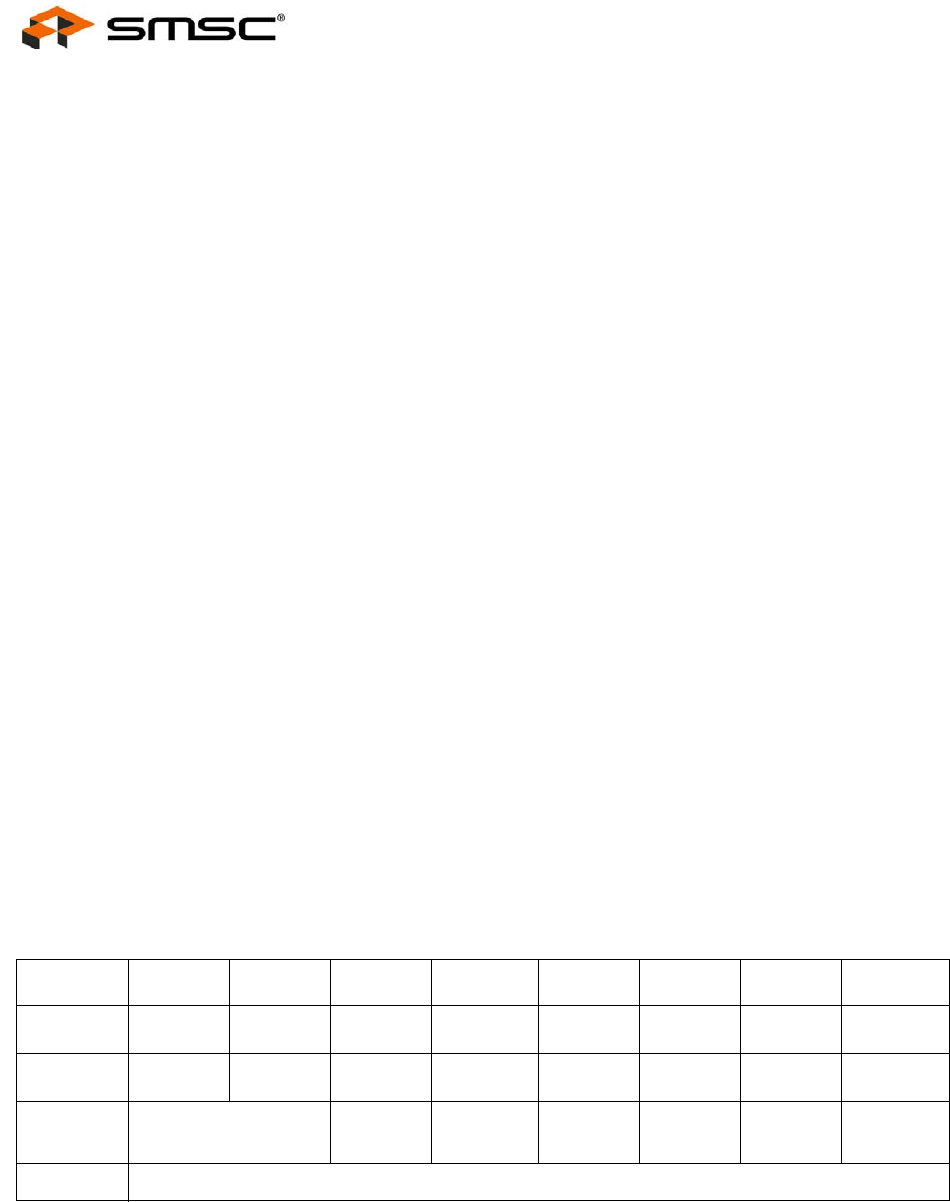

Table 10.8 EEPROM Configuration Bits

BYTE/BIT765 4 3210

Byte 8

BP_EN_

strap_1

FD_FC_

strap_1

manual_

FC_strap_1

manual_mdix

_strap_1

auto_mdix_

strap_1

speed_

strap_1

duplex_

strap_1

autoneg_

strap_1

Byte 9

BP_EN_

strap_2

FD_FC_

strap_2

manual_

FC_strap_2

manual_mdix

_strap_2

auto_mdix_

strap_2

speed_

strap_2

duplex_

strap_2

autoneg_

strap_2

Byte 10

LED_fun_strap[1:0] BP_EN_

strap_mii

FD_FC_

strap_mii

manual_FC

_strap_mii

speed_

strap_mii

duplex_pol_

strap_mii

SQE_test_

disable_strap

_mii

Byte 11

LED_en_strap[7:0]