Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 454 SMSC LAN9311/LAN9311i

DATASHEET

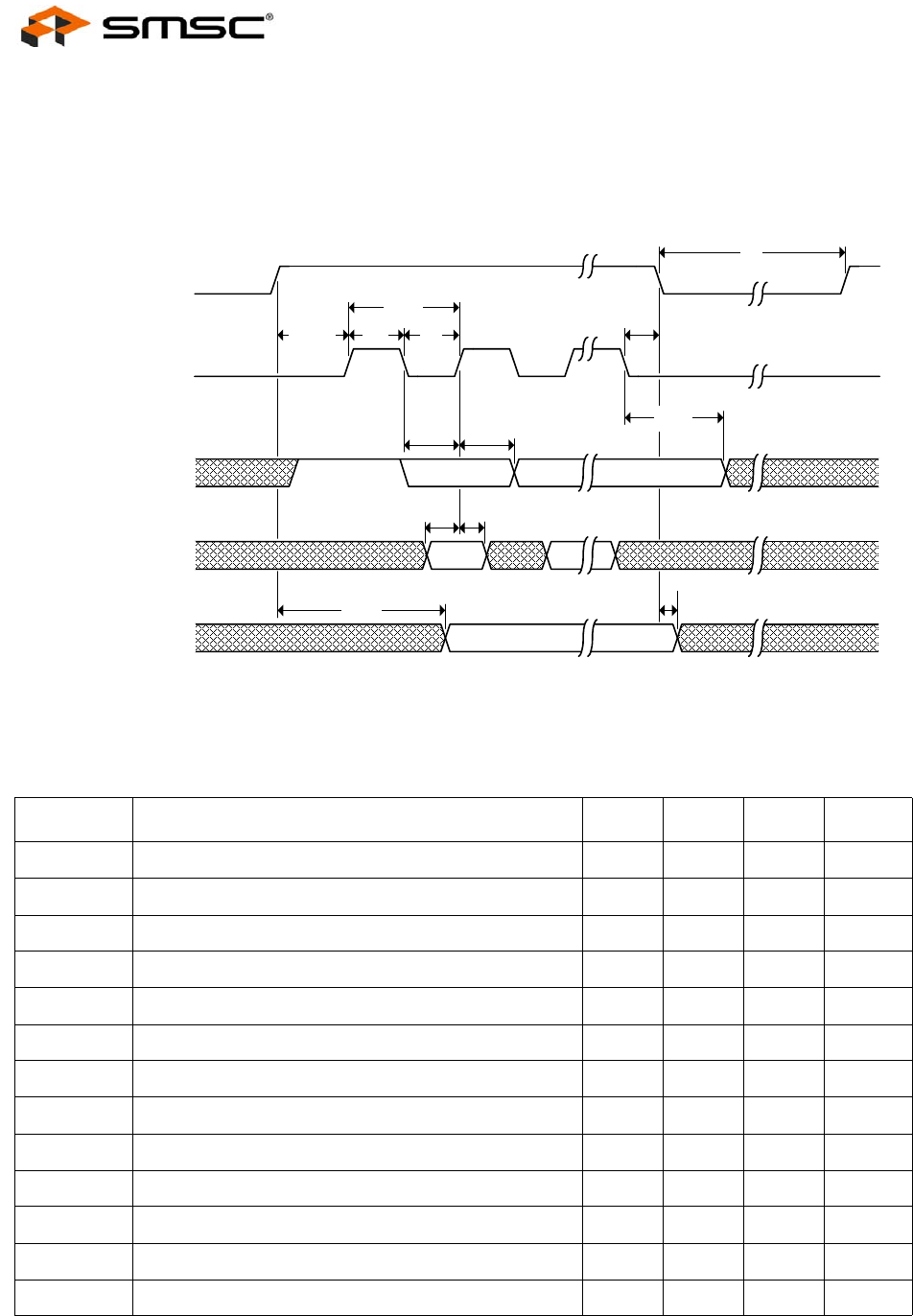

15.5.10 Microwire Timing

This section specifies the Microwire EEPROM interface timing requirements. Please refer to Section

10.2.3, "Microwire EEPROM," on page 145 for a functional description of this serial interface.

Figure 15.10 Microwire Timing

Table 15.14 Microwire Timing Values

SYMBOL DESCRIPTION MIN TYP MAX UNITS

t

ckcyc

EECLK cycle time 1110 1130 nS

t

ckh

EECLK high time 550 570 nS

t

ckl

EECLK low time 550 570 nS

t

cshckh

EECS high before rising edge of EECLK 1070 nS

t

cklcsl

EECLK falling edge to EECS low 30 nS

t

dvckh

EEDO valid before rising edge of EECLK 550 nS

t

ckhdis

EEDO disable after rising edge of EECLK 550 nS

t

dsckh

EEDI setup to rising edge of EECLK 90 nS

t

dhckh

EEDI hold after rising edge of EECLK 0 nS

t

ckldis

EECLK low to EEDO data disable 580 nS

t

cshdv

EEDI valid after EECS high (VERIFY) 600 nS

t

dhcsl

EEDI hold after EECS low (VERIFY) 0 nS

t

csl

EECS low 1070 nS

EECLK

EEDO

EEDI

EECS

t

ckldis

t

cshckh

EEDI (VERIFY)

t

ckh

t

ckl

t

ckcyc

t

cklcsl

t

csl

t

dvckh

t

ckhdis

t

dsckh

t

dhckh

t

dhcsl

t

cshdv