Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 123 Revision 1.4 (08-19-08)

DATASHEET

9.8 TX Data Path Operation

Data is queued for transmission by writing it into the TX Data FIFO. Each packet to be transmitted

may be divided among multiple buffers. Each buffer starts with a two DWORD TX command (TX

command ‘A’ and TX command ‘B’). The TX command instructs the LAN9311/LAN9311i on the

handling of the associated buffer. Packet boundaries are delineated using control bits within the TX

command.

The host provides a 16-bit Packet Tag field in the TX command. The Packet Tag value is appended

to the corresponding TX status DWORD. All Packet Tag fields must have the same value for all buffers

in a given packet. If tags differ between buffers in the same packet the TXE error will be asserted. Any

value may be chosen for a Packet Tag as long as all tags in the same Packet are identical. Packet

Tags also provide a method of synchronization between transmitted packets and their associated

status. Software can use unique Packet Tags to assist with validating matching status completions.

Note: The use of Packet Tags is not required by the hardware. This field can be used by the LAN

software driver for any application. Packet Tags is only one application example.

The Packet Length field in the TX command specifies the number of bytes in the associated packet.

All Packet Length fields must have the same value for all buffers in a given packet. Hardware

compares the Packet Length field and the actual amount of data received by the Ethernet controller.

If the actual packet length count does not match the Packet Length field as defined in the TX

command, the Transmitter Error (TXE) flag is asserted.

The LAN9311/LAN9311i can be programmed to start payload transmission of a buffer on a byte

boundary by setting the “Data Start Offset” field in the TX command. The “Data Start Offset” field points

to the actual start of the payload data within the first 8 DWORDs of the buffer. Data before the “Data

Start Offset” pointer will be ignored. When a packet is split into multiple buffers, each successive buffer

may begin on any arbitrary byte.

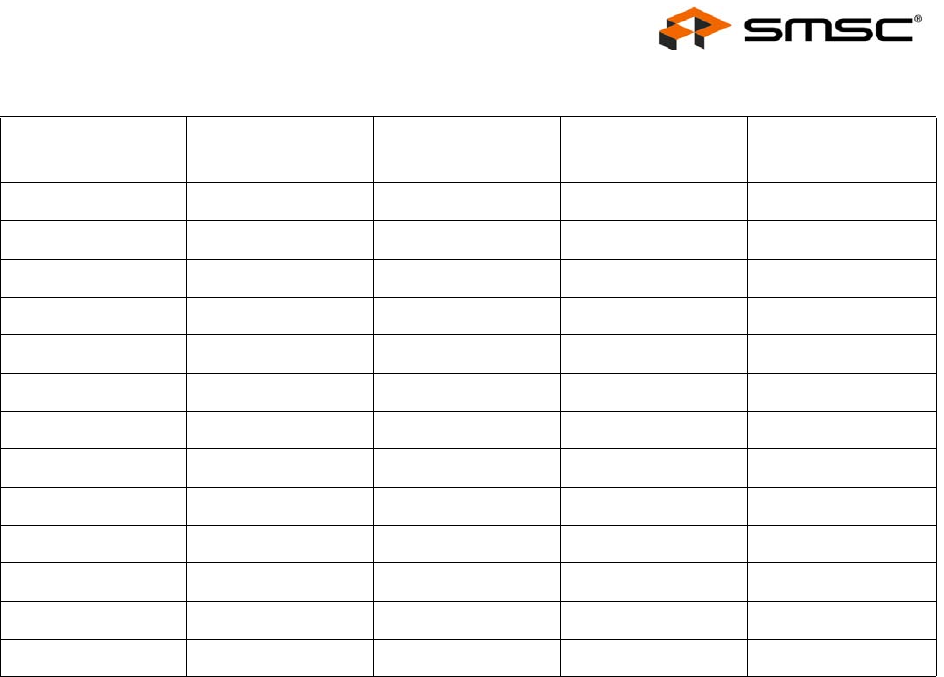

Table 9.9 Valid TX/RX FIFO Allocations

TX_FIF_SZ

TX DATA FIFO

SIZE (BYTES)

TX STATUS FIFO

SIZE (BYTES)

RX DATA FIFO

SIZE (BYTES)

RX STATUS FIFO

SIZE (BYTES)

2 1536 512 13440 896

3 2560 512 12480 832

4 3584 512 11520 768

5 4608 512 10560 704

6 5632 512 9600 640

7 6656 512 8640 576

8 7680 512 7680 512

9 8704 512 6720 448

10 9728 512 5760 384

11 10752 512 4800 320

12 11776 512 3840 256

13 12800 512 2880 192

14 13824 512 1920 128