Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 121 Revision 1.4 (08-19-08)

DATASHEET

Note: By convention, the right nibble of the left most byte of the Ethernet address (in this example,

the 2 of the 12h) is the most significant nibble and is transmitted/received first.

For more information on the EEPROM and EEPROM Loader, refer to Section 10.2, "I2C/Microwire

Master EEPROM Controller," on page 138.

9.7 FIFOs

The LAN9311/LAN9311i contains four host-accessible FIFOs (TX Status, RX Status, TX Data, and RX

Data) and two internal inaccessible Host MAC TX/RX MIL FIFO’s (TX MIL FIFO, RX MIL FIFO).

9.7.1 TX/RX FIFOs

The TX/RX Data and Status FIFOs store the incoming and outgoing address and data information,

acting as a conduit between the host bus interface (HBI) and the Host MAC. The sizes of these FIFOs

are configurable via the Hardware Configuration Register (HW_CFG) register to the ranges described

in Table 9.8. Refer to Section 9.7.3, "FIFO Memory Allocation Configuration" for additional information.

The the RX and TX FIFOs related register definitions can be found in section Section 14.2.2, "Host

MAC & FIFO’s".

The TX and RX Data FIFOs have the base address of 00h and 20h respectively. However, each FIFO

is also accessible at seven additional contiguous memory locations, as can be seen in Figure 14.1.

The Host may access the TX or RX Data FIFOs at any of these alias port locations, as they all function

identically and contain the same data. This alias port addressing is implemented to allow hosts to burst

through sequential addresses.

The TX and RX Status FIFOs can each be read from two register locations; the Status FIFO Port, and

the Status FIFO PEEK. The TX and RX Status FIFO Ports (48h and 40h respectively) will perform a

destructive read, popping the data from the TX or RX Status FIFO. The TX and RX Status FIFO PEEK

register locations (4Ch and 44h respectively) allow a non-destructive read of the top (oldest) location

of the FIFOs.

Proper use of the The TX/RX Data and Status FIFOs, including the correct data formatting is described

in detail in Section 9.8, "TX Data Path Operation," on page 123 and Section 9.9, "RX Data Path

Operation," on page 133.

9.7.2 MIL FIFOs

The MAC Interface Layer (MIL), within the Host MAC, contains a 2KB transmit and a 128 Byte receive

FIFO which are separate from the TX and RX FIFOs. These MIL FIFOs are not directly accessible

from the HBI. The differentiation between the TX/RX FIFOs and the TX/RX MIL FIFOs is that once the

transmit or receive packets are in the MIL FIFOs, the host no longer can control or access the TX or

RX data. The MIL FIFOs are essentially the working buffers of the Host MAC logic. In the case of

reception, the data must be moved into the RX FIFOs before the host can access the data. For TX

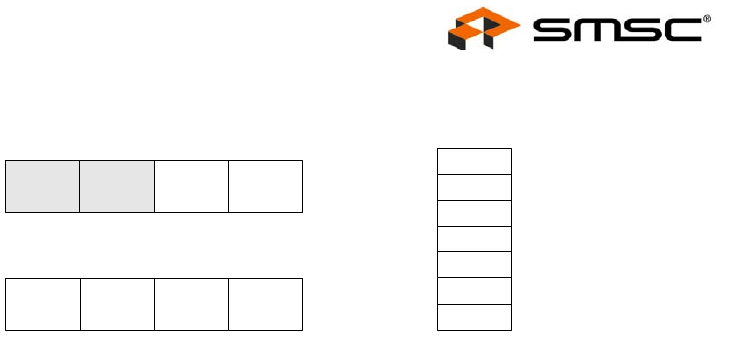

Figure 9.2 Example EEPROM MAC Address Setup

12h

07

34h

815

56h

1623

78h

2431

9AhBChxxxx

A5h

12h

34h

56h

78h

9Ah

BCh

00h

01h

02h

03h

04h

05h

06h

EEPROM

HMAC_ADDRH / SWITCH_MAC_ADDRH

0781516232431

HMAC_ADDRL / SWITCH_MAC_ADDRL