Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 290 SMSC LAN9311/LAN9311i

DATASHEET

Note 14.49 The default value of this bit is determined by the logical OR of the Auto-Negotiation strap

(autoneg_strap_1 for Port 1 PHY, autoneg_strap_2 for Port 2 PHY) and the speed select

strap (speed_strap_1 for Port 1 PHY, speed_strap_2 for Port 2 PHY). Essentially, if the

Auto-Negotiation strap is set, the default value is 1, otherwise the default is determined by

the value of the speed select strap. Refer to Section 4.2.4, "Configuration Straps," on

page 40 for more information.

Note 14.50 The default value of this bit is determined by the value of the Auto-Negotiation strap

(autoneg_strap_1 for Port 1 PHY, autoneg_strap_2 for Port 2 PHY). Refer to Section 4.2.4,

"Configuration Straps," on page 40 for more information.

Note 14.51 The default value of this bit is determined by the logical AND of the negation of the Auto-

Negotiation strap (autoneg_strap_1 for Port 1 PHY, autoneg_strap_2 for Port 2 PHY) and

the duplex select strap (duplex_strap_1 for Port 1 PHY, duplex_strap_2 for Port 2 PHY).

Essentially, if the Auto-Negotiation strap is set, the default value is 0, otherwise the default

is determined by the value of the duplex select strap. Refer to Section 4.2.4, "Configuration

Straps," on page 40 for more information.

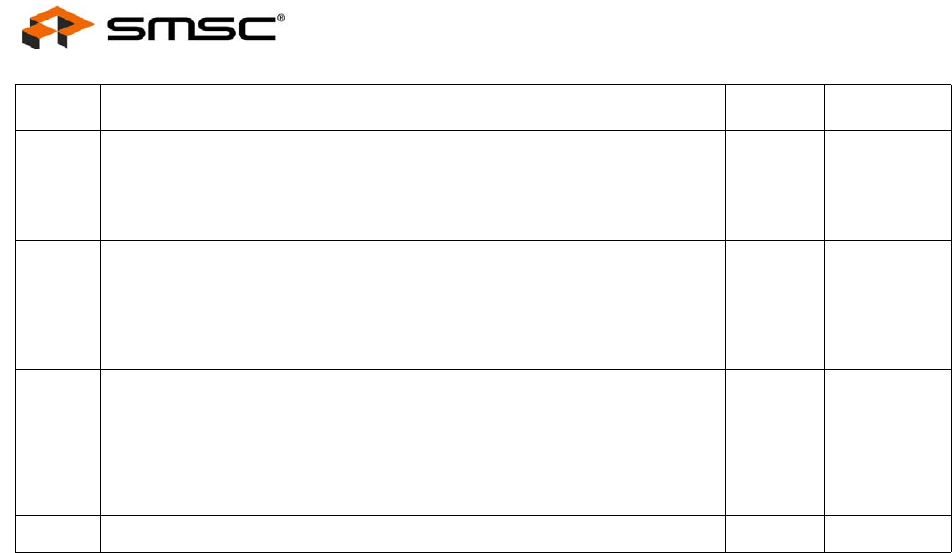

9

Restart Auto-Negotiation (PHY_RST_AN)

When set, this bit restarts the Auto-Negotiation process.

0: Normal operation

1: Auto-Negotiation restarted

R/W

SC

0b

8

Duplex Mode (PHY_DUPLEX)

This bit is used to set the duplex when the Auto-Negotiation (PHY_AN) bit

is disabled.

0: Half Duplex

1: Full Duplex

R/W Note 14.51

7

Collision Test Mode (PHY_COL_TEST)

This bit enables/disables the collision test mode of the Port x PHY. When

set, the collision signal is active during transmission. It is recommended that

this feature be used only in loopback mode.

0: Collision test mode disabled

1: Collision test mode enabled

R/W 0b

6:0

RESERVED RO -

BITS DESCRIPTION TYPE DEFAULT