Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 373 Revision 1.4 (08-19-08)

DATASHEET

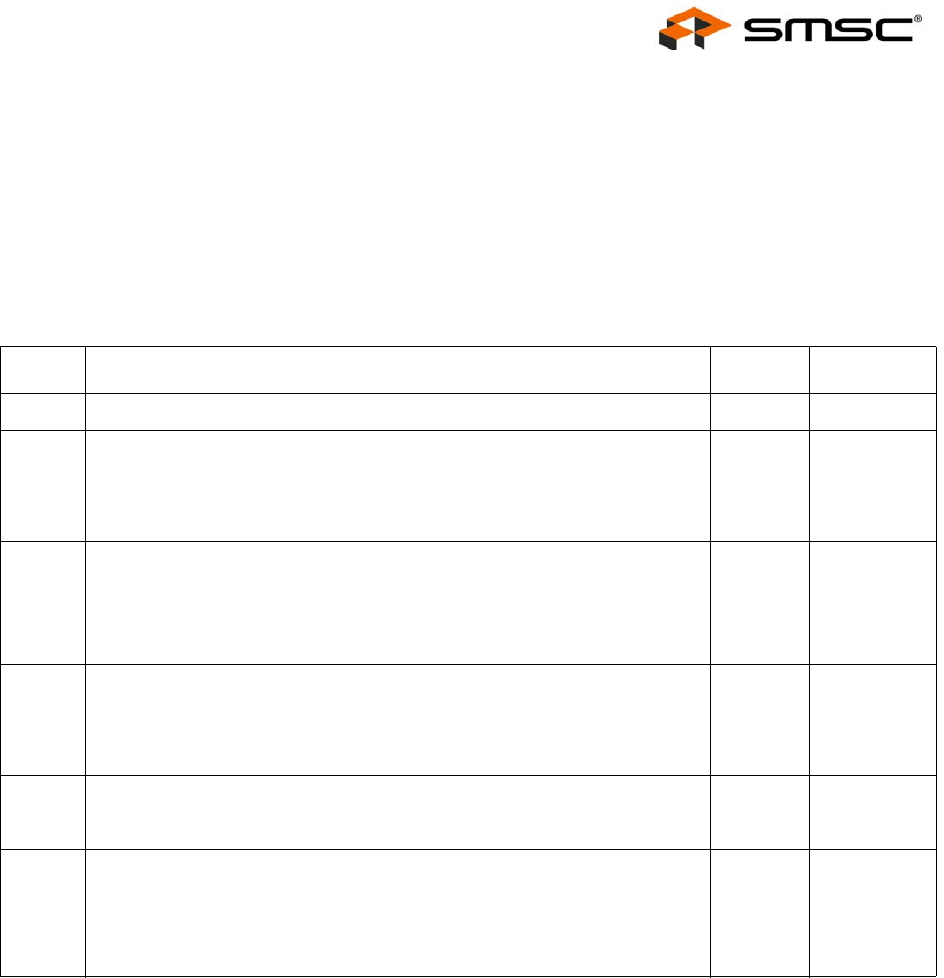

14.5.3.5 Switch Engine ALR Read Data 1 Register (SWE_ALR_RD_DAT_1)

This register is used in conjunction with the Switch Engine ALR Read Data 0 Register

(SWE_ALR_RD_DAT_0) to read the ALR table. It contains the last 32 bits of the ALR entry and is

loaded via the Get First Entry or Get Next Entry commands in the Switch Engine ALR Command

Register (SWE_ALR_CMD). This register is only valid when either of the Valid or End of Table bits are

set.

Register #: 1806h Size: 32 bits

BITS DESCRIPTION TYPE DEFAULT

31:25 RESERVED RO -

24

Valid

This bit is cleared when the Get First Entry or Get Next Entry bits of the

Switch Engine ALR Command Register (SWE_ALR_CMD) are written. This

bit is set when a valid entry is found in the ALR table. This bit stays cleared

when the top of the ALR table is reached without finding an entry.

RO 0b

23

End of Table

This bit indicates that the end of the ALR table has been reached and further

Get Next Entry commands are not required.

Note: The Valid bit may or may not be set when the end of the table is

reached.

RO 0b

22

Static

Indicates that this entry will not be removed by the aging process. When this

bit is cleared, this entry will be automatically removed after 5 to 10 minutes

of inactivity. Inactivity is defined as no packets being received with a source

address that matches this MAC address.

RO 0b

21

Filter

When set, indicates that packets with a destination address that matches

this MAC address will be filtered.

RO 0b

20:19

Priority

These bits indicate the priority that is used for packets with a destination

address that matches this MAC address. This priority is only used if the

Static bit of this register is set, and the DA Highest Priority (bit 5) in the

Switch Engine Global Ingress Configuration Register

(SWE_GLOBAL_INGRSS_CFG) register is set.

RO 00b