Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 304 SMSC LAN9311/LAN9311i

DATASHEET

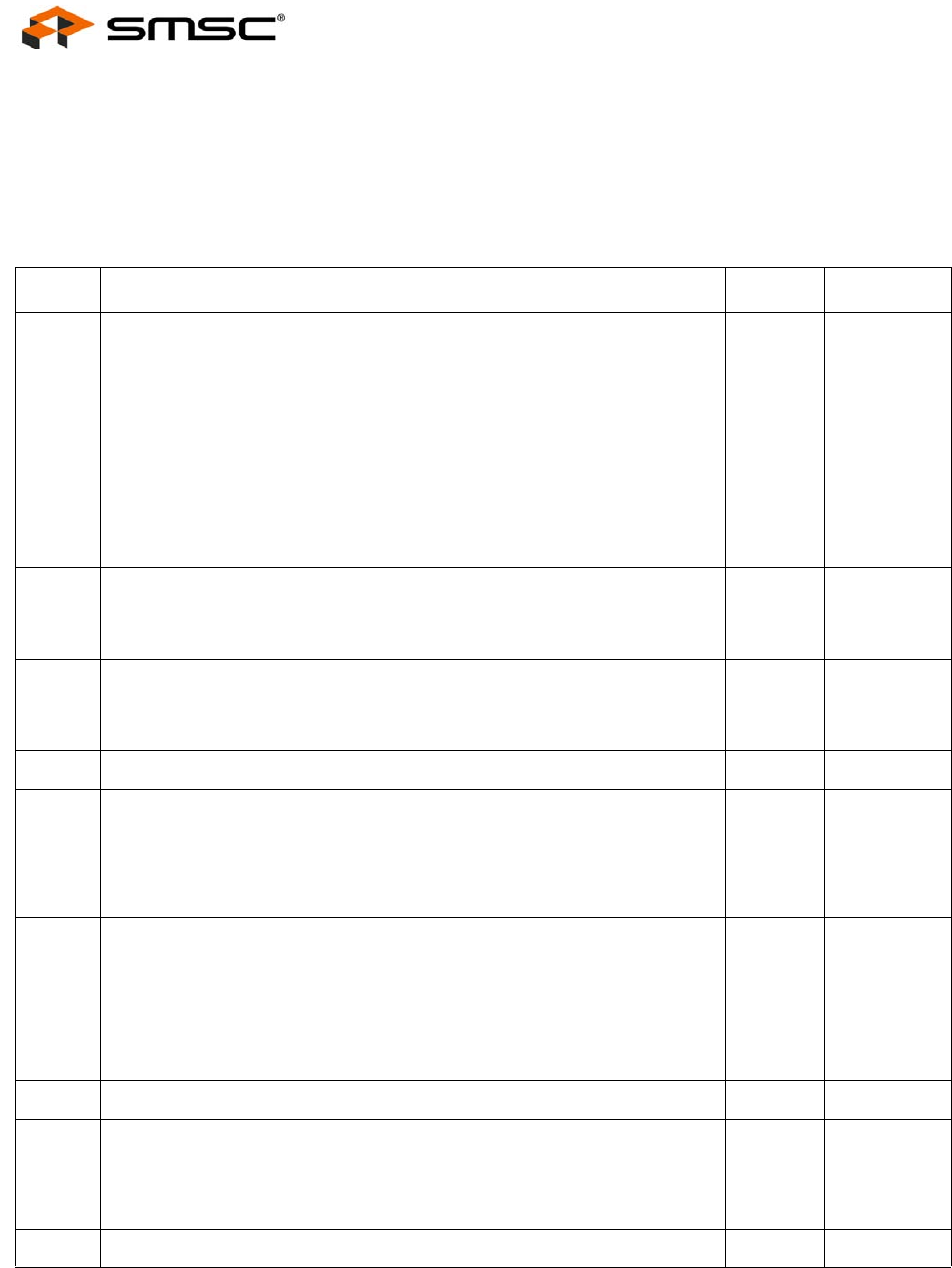

14.4.2.10 Port x PHY Special Control/Status Indication Register (PHY_SPECIAL_CONTROL_STAT_IND_x)

This read/write register is used to control various options of the Port x PHY.

Note 14.61 Register bits designated as NASR are reset when the Port x PHY Reset is generated via

the Reset Control Register (RESET_CTL). The NASR designation is only applicable when

the Reset (PHY_RST) bit of the Port x PHY Basic Control Register

(PHY_BASIC_CONTROL_x) is set.

Index (decimal): 27 Size: 16 bits

BITS DESCRIPTION TYPE DEFAULT

15 Auto-MDIX Control (AMDIXCTRL)

This bit is responsible for determining the source of Auto-MDIX control for

Port x. When set, the Manual MDIX and Auto MDIX straps

(manual_mdix_strap_1/auto_mdix_strap_1 for Port 1 PHY,

manual_mdix_strap_2/auto_mdix_strap_2 for Port 2 PHY) are overridden,

and Auto-MDIX functions are controlled using bit 14 (AMDIXEN) and bit 13

(AMDIXSTATE) of this register. When cleared, Auto-MDIX functionality is

controlled by the Manual MDIX and Auto MDIX straps by default. Refer to

Section 4.2.4, "Configuration Straps," on page 40 for configuration strap

definitions.

0: Port x Auto-MDIX determined by strap inputs

1: Port x Auto-MDIX determined by bits 14 and 13

R/W

NASR

Note 14.61

0b

14

Auto-MDIX Enable (AMDIXEN)

When bit 15 (AMDIXCTRL) of this register is set, this bit is used in

conjunction with bit 13 (Auto-MDIX State) to control the Port x Auto-MDIX

functionality as shown in Table 14.11.

R/W

NASR

Note 14.61

0b

13

Auto-MDIX State (AMDIXSTATE)

When bit 15 (AMDIXCTRL) of this register is set, this bit is used in

conjunction with bit 14 (Auto-MDIX Enable) to control the Port x Auto-MDIX

functionality as shown in Table 14.11.

R/W

NASR

Note 14.61

0b

12

RESERVED RO -

11

SQE Test Disable (SQEOFF)

This bit controls the disabling of the SQE test (Heartbeat). SQE test is

enabled by default.

0: SQE test enabled

1: SQE test disabled

R/W

NASR

Note 14.61

0b

10

Receive PLL Lock Control (VCOOFF_LP)

This bit controls the locking of the receive PLL. Setting this bit to 1 forces

the receive PLL 10M to lock on the reference clock at all times. When in this

mode, 10M data packets cannot be received.

0: Receive PLL 10M can lock on reference or line as needed (normal

operation)

1: Receive PLL 10M locked onto reference clock at all times

R/W

NASR

Note 14.61

0b

9:5

RESERVED RO -

4

10Base-T Polarity State (XPOL)

This bit shows the polarity state of the 10Base-T.

0: Normal Polarity

1: Reversed Polarity

RO 0b

3:0

RESERVED RO -