Overview: Additional Information

PmT1 and PmE1 User’s Manual 10002367-02

1-4

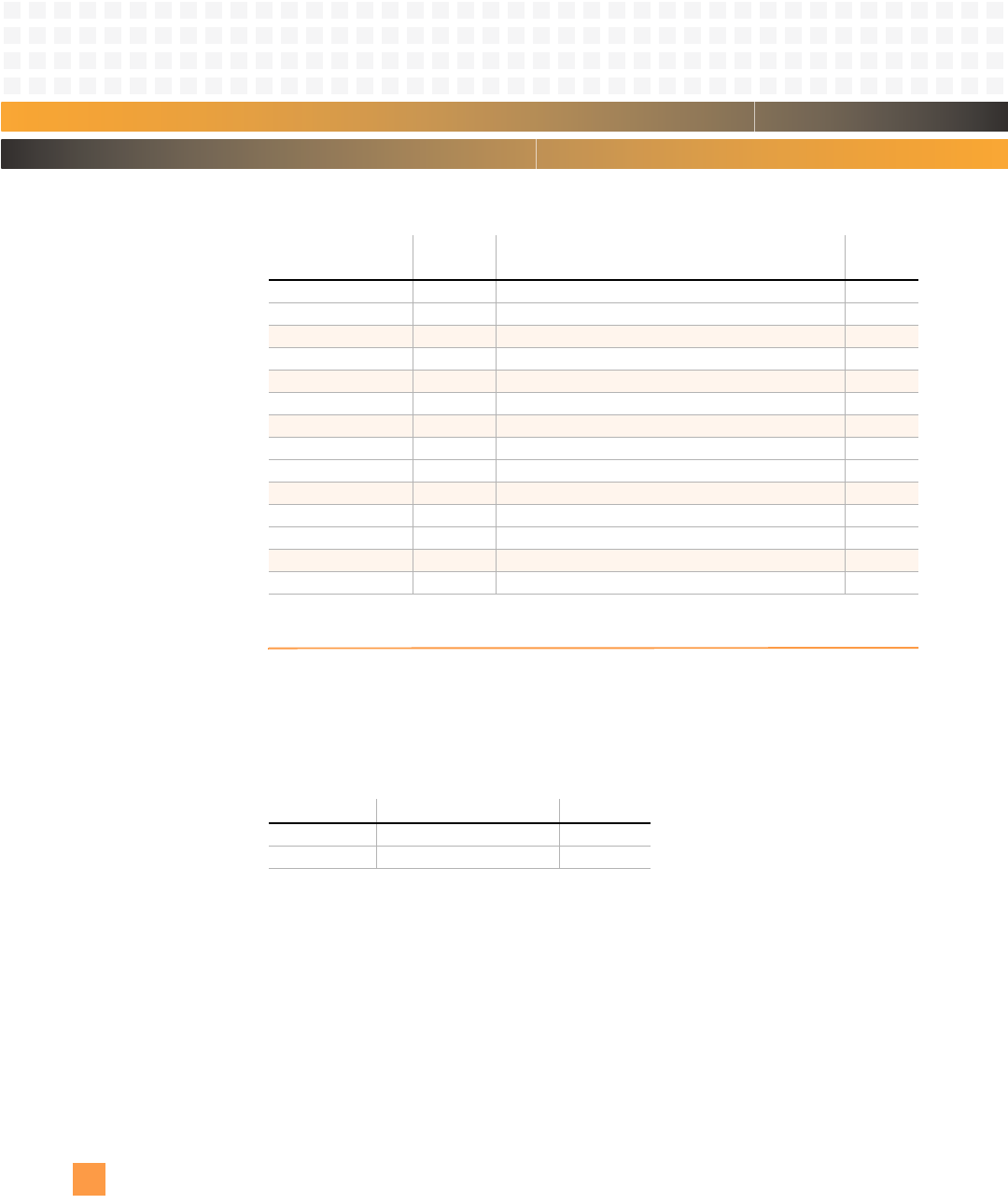

Table 1-1: Address Summary

ADDITIONAL INFORMATION

This section lists the PmT1 and PmE1 hardware’s regulatory certifications and briefly dis-

cusses the terminology and notation conventions used in this manual. It also lists general

technical references.

Mean time between failures (MTBF) is listed in the following table:

Table 1-2: MTBF Hours

Product Certification

The PmT1 and PmE1 hardware has been tested to comply with various safety, immunity,

and emissions requirements as specified by the Federal Communications Commission

(FCC), Underwriters Laboratories (UL), and others. The following table summarizes this

compliance:

Physical Address

(hex):

Access

Mode: Description:

See

Page:

FFF0,0000 R Flash/ROM Socket 4-1

FF00,0000 R/W CPU registers 3-2

C101,0000 — reserved —

C100,0000 R/W PMC/PCI Interface registers 7-2

C000,0200 — reserved —

C000,0180 R Board Configuration register 4-3

C000,0080 — reserved —

C000,000C R Conventional Interrupt register 3-4

C000,0000 R Interrupt Vector register 3-4

8000,0000 — reserved —

6000,0000 R/W PCI I/O Space 7-2

4000,000 R/W PCI Memory Space 7-2

C101,0000 — reserved —

0000,0000 R/W DRAM 4-2

Product Calculation Method: Hours:

PmT1 Bellcore Issue 5 344,234

PmE1 Telecordia Issue 1 1,333,573