10002367-02 PmT1 and PmE1 User’s Manual

3-1

Section 3

Central Processing Unit

The PmT1 and PmE1 module uses the Freescale MPC860P PowerQUICC™ microprocessor

installed as its CPU. The MPC860P combines an embedded PowerPC™ core with features of

the QUICC MC68360 communications processor module (CPM). This chapter is an overview

of the processor logic on the PmT1 and PmE1. It includes information on the CPU, excep-

tion handling, and processor reset.

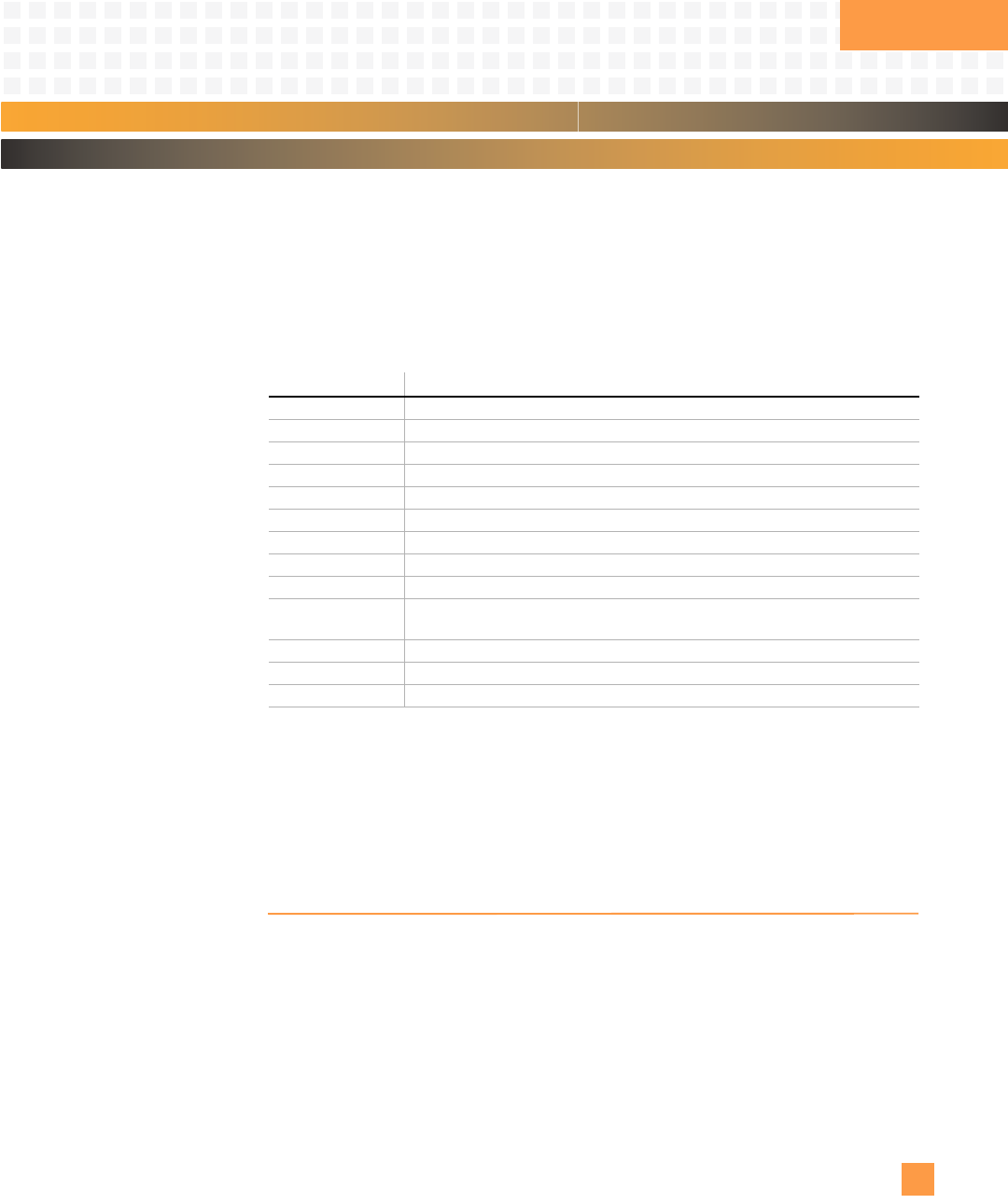

Table 3-1: MPC860P Features

Beyond the usual CPU functions, the MPC860P provides:

• A DRAM controller is contained in the system interface unit (SIU). The memory

controller is described in the “On-card DRAM”, Section .

• Four high-speed SCC serial ports are supported by the CPM. The serial interface is

described in Chapter 5

MPC860P INITIALIZATION

Some of the MPC860P registers must be initialized with Emerson-specific values. The val-

ues in the following tables assume a PmT1 and PmE1 configuration of 9600 baud, 40-MHz

and CPU speed.

The relevant special purpose registers on the MPC860P are accessed with the Move to Spe-

cial Registers (mtspr) and the Move from Special Registers (mfspr) instructions.

Feature: Description:

Instruction Set 32-bit

System Clock Rate 80 MhZ

Data Bus 32-bit

Address Bus 32-bit

Cache 16K instruction, 8K data

MMU 32-entr y instruction and data Translation Look-aside Buffer (TLB)

Dual-port RAM 8K

ATM 10/100 base-T Ethernet, QMC microcode for multichannel HDLC support

Serial Channel four SCCs, two SMCs, one SPI and on I

2

C interface

System Interface

Unit (SIU)

Memory controller, internal and external bus interface units, real-time clock,

PCMIA-ATA interface, and JTAG TAP

DMA channels 16 virtual SDMA and 2 IDMA

Dynamic bus sizing 8-, 16-, or 32-bits

Voltages 3.3V operation with 5V TTL compatibility