Serial I/O: The Communications Processor Module

10002367-02 PmT1 and PmE1 User’s Manual

5-3

CPM Interrupt Handling

The CPM RISC controller generates interrupts through the interrupt controller to the CPU.

The interrupt vector is provided by the CPU.

The interrupt controller is the focal point for all internal and external interrupt requests by

the CPM. It handles up to 28 interrupt sources (12 external, 16 internal) which may be

assigned to a programmable interrupt level (1, 3, 5, 7). The priority in which interrupt

sources are serviced is generally fixed (see the MPC860 PowerQUICC™ User’s Manual), but

some flexibility is provided to modify the priority structure, particularly with respect to the

SCCs.

Dual-Port RAM

The CPM has 8KB of SRAM configured as dual-port memory. It can be accessed by the RISC

processor, the CPU, IDMAs, and SDMAs. The dual-port RAM has the following uses–any two

of which can occur simultaneously:

• Store parameters associated with the SCCs and IDMAs

• Store buffer descriptors (describe the location of data buffers)

• Store data from the serial channels

• Store RAM microcode for the RISC processor

• Scratchpad RAM space for the user program

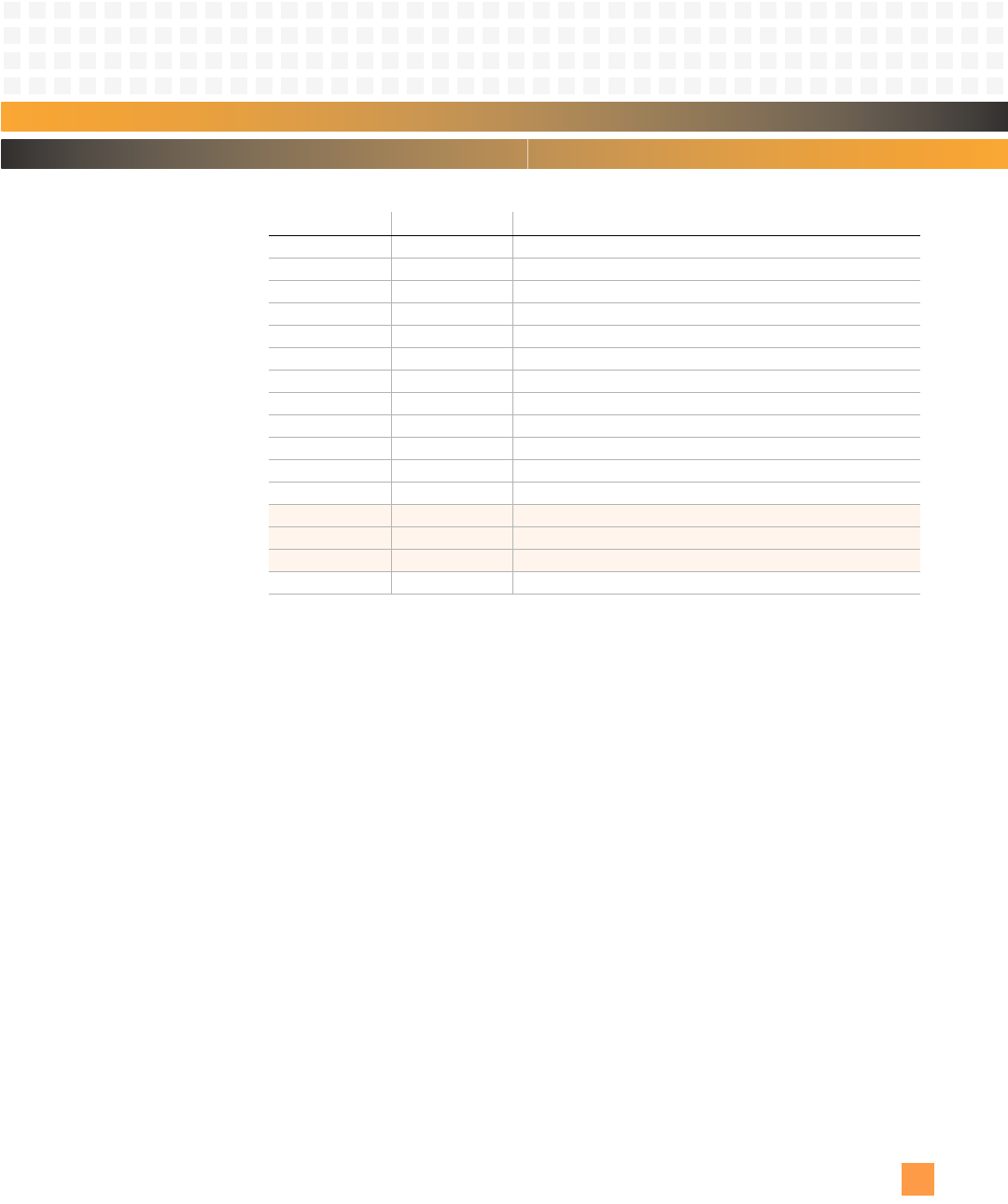

4 SCC1 Reception

5 SCC1 Transmission

6 SCC2 Reception

7 SCC2 Transmission

8 SCC3 Reception

9 SCC3 Transmission

10 SCC4 Reception

11 SCC4 Transmission

12 SMC1 Reception

13 SMC1 Transmission

14 SMC2 Reception

15 SMC2 Transmission

16 reserved

17 reserved

18 reserved

Lowest 19 RISC Timers

Priority: Function: Description: