Central Processing Unit: MPC860P Exception Handling

10002367-02 PmT1 and PmE1 User’s Manual

3-3

MPC860P EXCEPTION HANDLING

Each type of CPU exception transfers control to a different address in the vector table. The

vector table normally occupies the first 8-kilobytes of RAM (with a base address of

0000,0000

16

) or flash (with a base address of FFF0,0000

16

). An unassigned vector position

may be used to point to an error routine or for code or data storage.

Tab le 3 -4 lists the

exceptions recognized by the MPC860P in the order of their priority

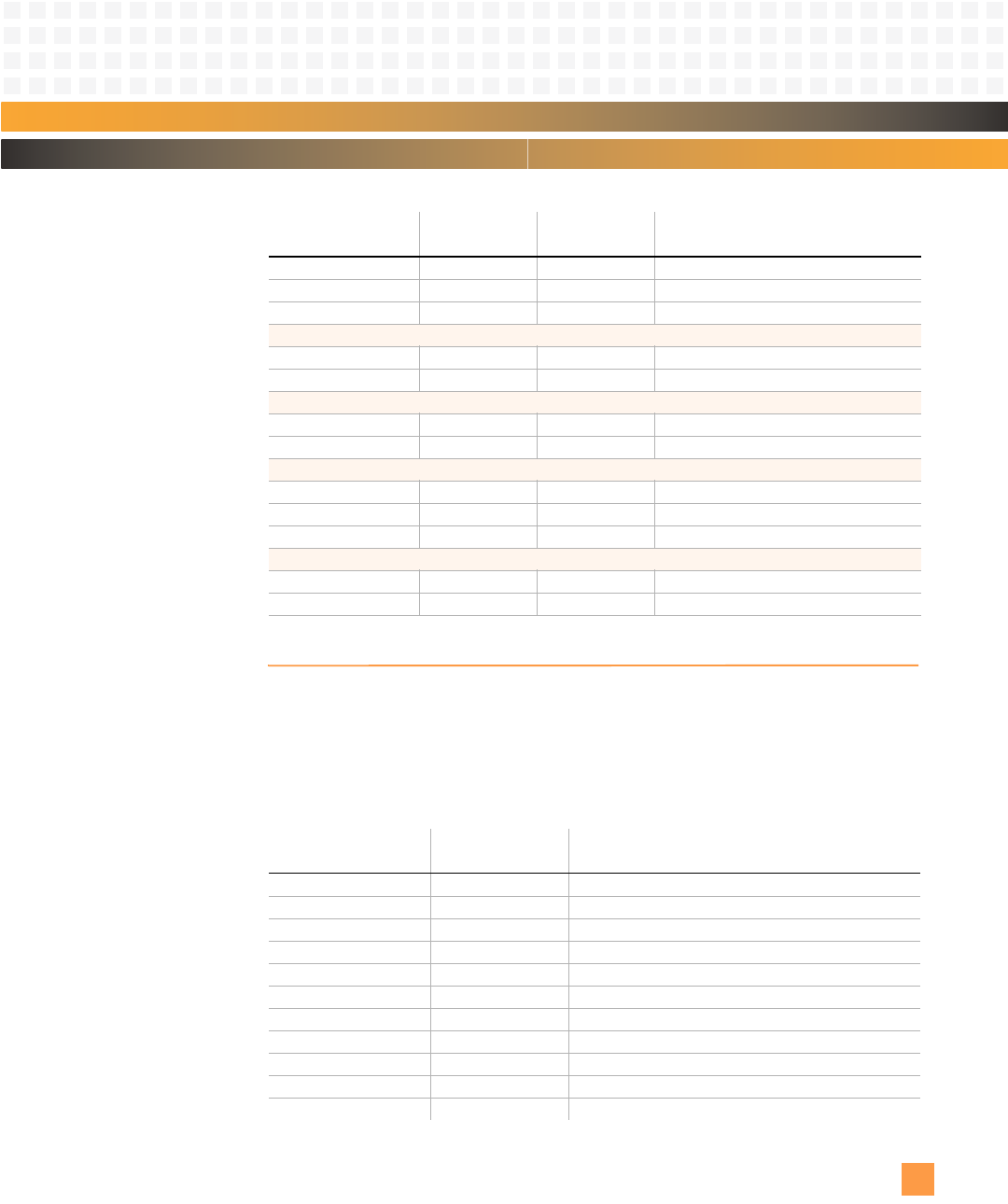

Table 3-4: MPC860P Exceptions

FF00,0950 PADIR 000A Port A data direction register

FF00,0952 PAPAR 0000 Port A pin assignment register

FF00,0954 PADDR 0000 Port A open drain register

BRGs

FF00,09F0 BRGC1 10144 BRG1 configuration register

FF00,09F4 BRGC2 10144 BRG2 configuration register

SMCs

FF00,0A82 SMCMR1 4823 SMC1 mode register

FF00,0A92 SMCMR2 4823 SMC2 mode register

PIP

FF00,0AB8 PBDIR 0030 Port B data direction register

FF00,0ABC PBPAR 00C0 Port B pin assignment register

FF00,0AC2 PBODR 0010 Port B open drain register

SI

FF00,0AE0 SIMODE 1000,0000 SI mode register

FF00,0AEC SICR 0000,0000 SI clock route

Exception:

Vector Address

Hex Offset: Notes:

Development port NMI 01F00 Highest priority

NMI reset 00100

Tr ace 0 0D 00

Instruction TLB miss 01100

Instruction TLB error 01300

Machine check 00200

Instruction breakpoint 01D00

Software emulation 01000

Alignment 00600

System call 00C00

Data TLB miss 01200

Physical

Address (hex): Register:

Required

Hex Format: Description: (continued)