Monitor: Power-up Diagnostic/Test Commands

10002367-02 PmT1 and PmE1 User’s Manual

8-17

POWER-UP DIAGNOSTIC/TEST COMMANDS

The following on-card functional tests are available to be run at any time, including power-

up and reset. The nonvolatile configuration memory can be used to enable or disable the

execution of these tests on power-up and reset (see the nvdisplay command’s Misc group

in

Tab le 8 -1 ).

The results of the tests are stored at an offset of 0x60 in the I

2

C EEPROM. To read the

PASS/FAIL flags, do four byte reads from the EEPROM at 0x60, 0x61, 0x62, and 0x63. The

byte at 0x60 should contain the magic number 0xa5 indicating that the device is functional

and that PASS/FAIL reporting is supported. The values for the long word when a failure

occurs are listed in

Ta ble 8 -3 .

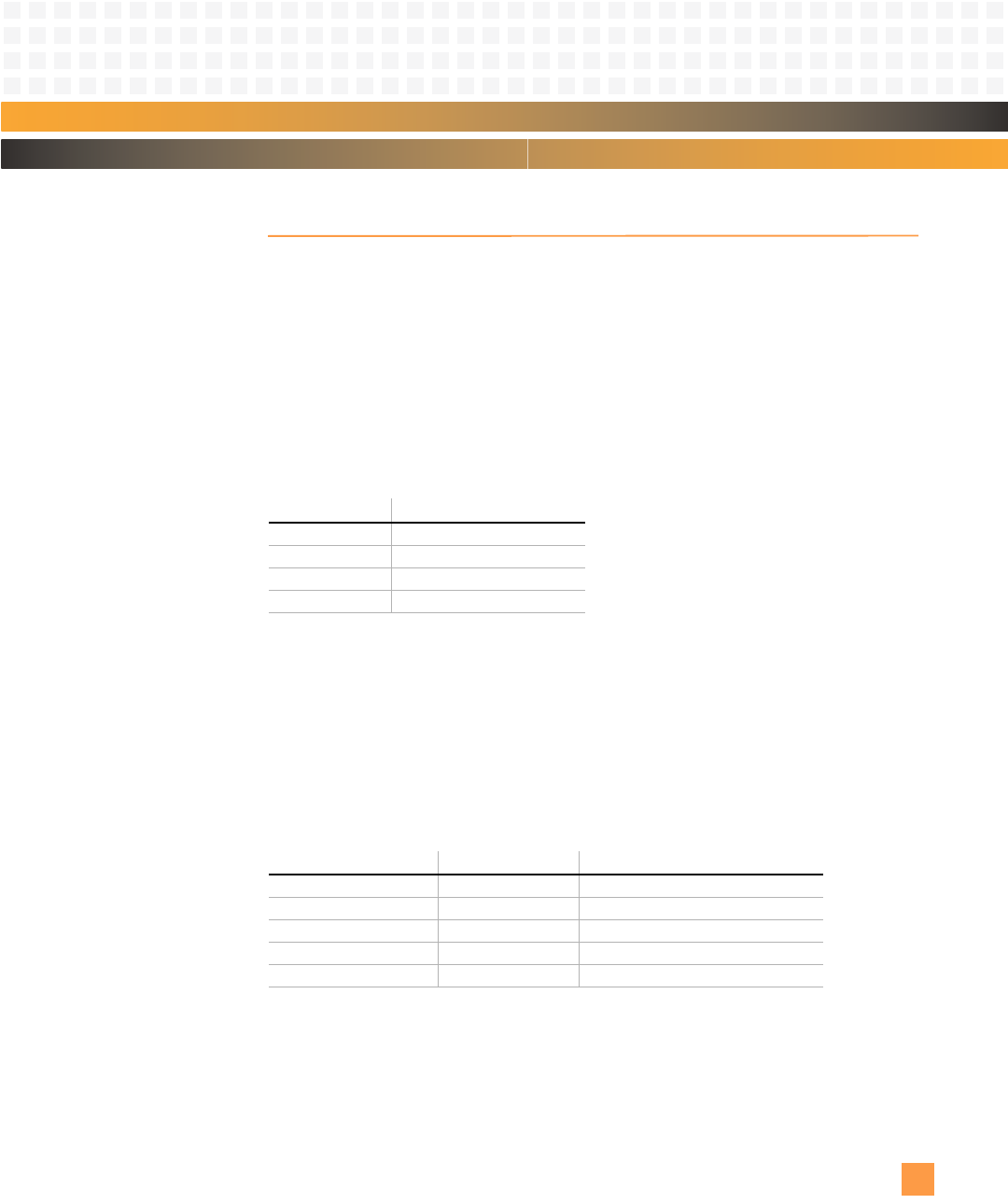

Table 8-3: NVRAM Power-up Diagnostic PASS/FAIL Flags

The power-up PASS/FAIL flags are also written to PLX Mailbox 0. The module writes the

progress and PASS/FAIL status of each of its power-up tests to PCI so that the baseboard

can determine the power-up status of the module and proceed accordingly. At the conclu-

sion of power-up, the same magic number (0xa5) used in the NVRAM PASS/FAIL flags is

written to the least significant bit (LSB) of PLX Mailbox 0. The PLX Mailbox 0 register can be

polled until the magic number is displayed and then checked to see if there are any fail

mask bits set. The following bits in

Tab le 8 -4 are used to indicate the power-up test

sequence and failure.

Table 8-4: PLX Mailbox 0 Sequence and Fail Mask Bits

For example, if the module had a memory failure, the PLX Mailbox 0 register would contain

0x0B000400. For parity and DRAM failures, the same register would contain 0x0A000600.

The magic number 0xa5 will not be in the LSB of the PLX Mailbox 0 register because if a

memory error is encountered, then the debug monitor is entered. If all power-up tests

pass, the PLX Mailbox 0 will be 0xA5000000.

Test: Value Read on Failure:

Serial 0xa5000001

Counter/Timer 0xa5000002

Cache 0xa5000010

EEPROM 0xa5000020

Power-up Test: Sequence Bit: Fail Mask Bit:

Counter/Timer 0x02000000 0x00000002

Cache 0x05000000 0x00000010

EEPROM 0x06000000 0x00000020

Parity DRAM Memory 0x0A000000 0x00000200

Data DRAM Memory 0x0B000000 0x00000400