Serial I/O: The Communications Processor Module

PmT1 and PmE1 User’s Manual 10002367-02

5-2

CPM Register Initialization Format

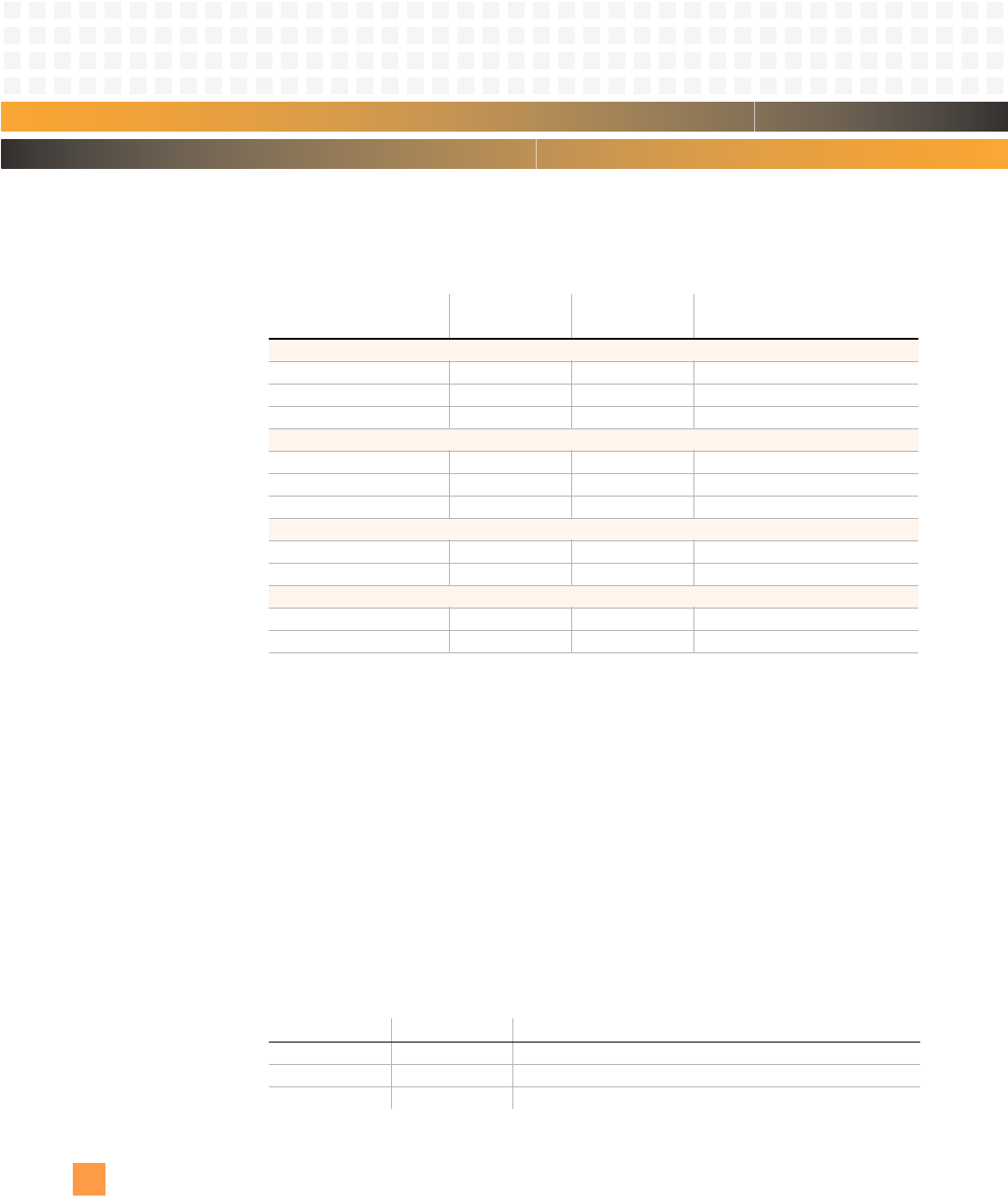

Some of the CPM registers must be initialized as described in Tabl e 5 -2 .

Table 5-2: CPM Initialization Values

RISC Controller

The RISC controller manages the serial interface to the CPM. It services all I/O requests,

allowing the CPU on the PmT1 and PmE1 module to dedicate compute time to other tasks.

The RISC controller implements user-chosen protocols, manages serial DMA transfers and

independent DMA transfers (optionally), and maintains 16 timers for use in application soft-

ware. See

Ta bl e 5 -3 for the RISC controller processing priority. It can communicate with the

external processor using the following methods:

• Parameters exchanged through dual-port RAM

• External processor executes special commands via the RISC controller

• RISC controller generates interrupts through the interrupt controller

External processor reads the controller's status/event registers

Table 5-3: RISC Controller Processing Priority

Physical Address

(hex): Acronym:

Required

Hex Format: Description:

Input/Output Port

FF00,0950 PADIR 000A Port A Data Direction register

FF00,0952 PAPAR 0000 Port A Pin Assignment register

FF00,0954 PAODR 0000 Port A Open Drain register

BRGs

FF00,09F0 BRGC1 10144 BRG1 Configuration register

FF00,09F4 BRGC2 10144 BRG2 Configuration register

FF00,0AC2 PBODR 0010 Port B Open Drain register

SMCs

FF00,0A82 SMCMR1 4823 SMC1 mode register

FF00,0A92 SMCMR2 4823 SMC2 mode register

SI

FF00,0AE0 SIMODE 1000,0000 SI Mode register

FF00,0AEC SICR 0000,0000 SI Clock route

Priority: Function: Description:

Highest 1 Reset in RISC Processor Command register or System Reset

2SDMA Bus Error

3 Commands issued in the RISC Processor Command register