Central Processing Unit: System Interface Unit (SIU)

PmT1 and PmE1 User’s Manual 10002367-02

3-4

CPU Interrupts

The logic on the PmT1 and PmE1 module receive external interrupts LSERR* and LINTo*

from the PCI9060ES chip. These interrupts are combined on IRQ7*, which is the only exter-

nal interrupt input used on the MPC860P.

The Conventional Interrupt register and the Interrupt Vector register are available to moni-

tor the status of the external interrupts. These registers are byte wide and read-only.

Attempts to read these registers with data sizes greater than a byte does not result in a bus

error.

The Conventional Interrupt register at C000,000C

16

indicates which PCI9060ES interrupts

are active. If bit 5 is one, LSERR* is active. If bit 4 is one, LINTo* is active. All other bits in this

register read as zero.

Bits (4:2) of the Interrupt Vector register (at C000,0000

16

) store the vector of the highest

priority external interrupt that is pending. The vector for LSERR* is 100

2

; the vector for

LINTo* is 011

2

. The vector 000

2

indicates that no interrupt is pending.

Internal interrupt sources including the hardware bus monitor, the software watchdog

timer, the periodic interrupt timer (PIT), the real-time clock, and the CPM may each be

assigned to a particular interrupt level in software. Interrupt levels may be programmed for

logic low or negative edge assertion.

SYSTEM INTERFACE UNIT (SIU)

The SIU provides the MPC860P with system configuration and monitoring features. In par-

ticular, two system timers are described in the following subsections. The memory control-

ler is also part of the SIU but is described in the “On-card DRAM”, Section .

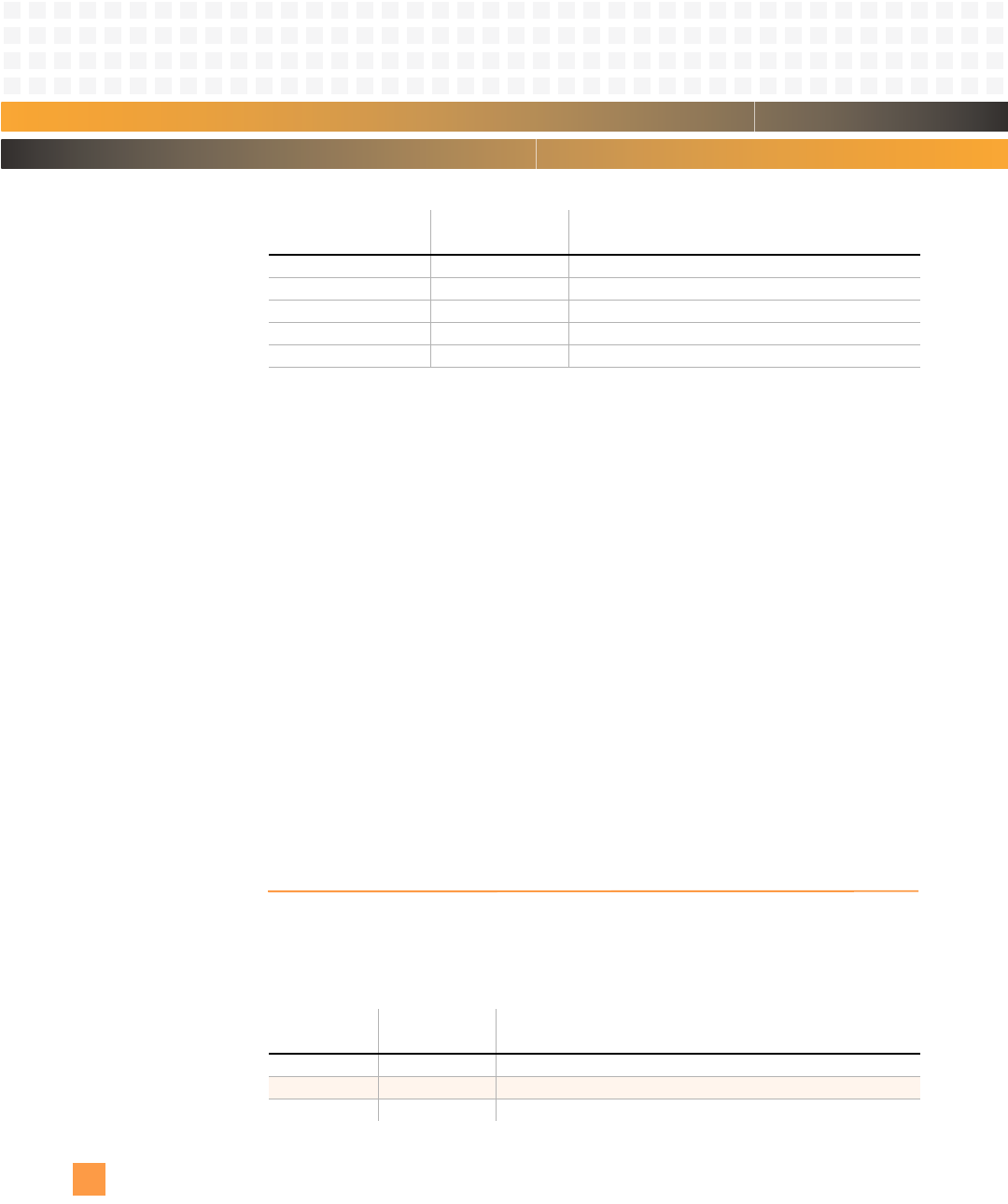

Table 3-5: MPC860P SIU Register Block Map

Data TLB error 01400

Data breakpoint 01C00

Peripheral breakpoint 01E00

External interrupt 00500

Decrementer Decrementer Lowest priority

Physical Hex

Address: Acronym: Register Block Name:

FF00,0000 SIU General System Interface Unit

FF00,0080 — reserved

FF00,0100 MEMC Memory controller

Exception:

Vector Address

Hex Offset: Notes: (continued)