Extensible Firmware Interface Specification

12-2 12/01/02 Version 1.10

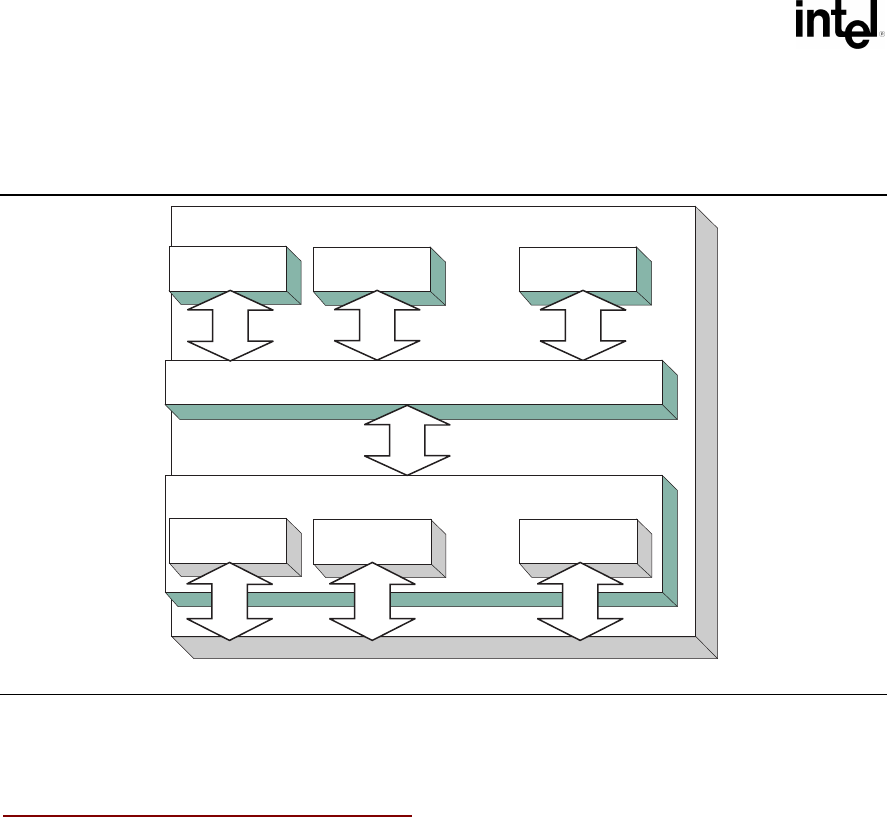

A platform can be viewed as a set of processors and a set of core chipset components that may

produce one or more host buses. Figure 12-1 shows a platform with n processors (CPUs in the

figure), and a set of core chipset components that produce m host bridges.

OM13150

Core Chipset Components

. . .

. . .

CPU 2

CPU

n

Front Side Bus

CPU 1

HB 2

HB

m

HB 1

Figure 12-1. Host Bus Controllers

Simple systems with one PCI Host Bus Controller will contain a single instance of the

EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL

. More complex system may contain multiple

instances of this protocol. It is important to note that there is no relationship between the number of

chipset components in a platform and the number of EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL

instances. This protocol abstracts access to a PCI Root Bridge from a software point of view, and it

is attached to a device handle that represents a PCI Root Bridge. A PCI Root Bridge is a chipset

component(s) that produces a physical PCI Bus. It is also the parent to a set of PCI devices that

share common PCI I/O, PCI Memory, and PCI Prefetchable Memory regions. A PCI Host Bus

Controller is composed of one or more PCI Root Bridges.