Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

107 Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

5.7 Optical Module Interface

This section describes the connection of the IXF1104 MAC ports to an Optical Module Interface

and details the minimal connections that are supported for correct operation. The registers used for

write control and read status information are documented.

The Optical Module Interface allows the IXF1104 MAC a seamless connection to the Small Form

Factor Optical Modules (SFP) that form the system’s physical media connection, eliminating the

need for any FPGAs or CPUs to process data. All required optical module information is available

to the system CPU through the IXF1104 MAC CPU interface, leading to a more integrated,

reliable, and cost-effective system.

The IXF1104 MAC supports all the functions required for the Small Form Factor pluggable Multi-

Source Agreement (MSA).

There are specific mechanical and electrical requirements for the size, form factor, and connections

supported on all Optical Module Interfaces. There are also specific requirements for each Optical

Module Interface that supports a particular media requirement or interface configuration. These

requirements are detailed in the relevant specifications or manufacturers’ datasheets.IXF1104

MAC

5.7.1 Intel® IXF1104 MAC-Supported Optical Module Interface Signals

To describe the Optical Module Interface operation, three supported signal subgroups are required,

allowing a more explicit definition of each function and implementation. The three subgroups are

as follows:

• High-Speed Serial Interface

• Low-Speed Status Signaling Interface

• I²C Module Configuration Interface

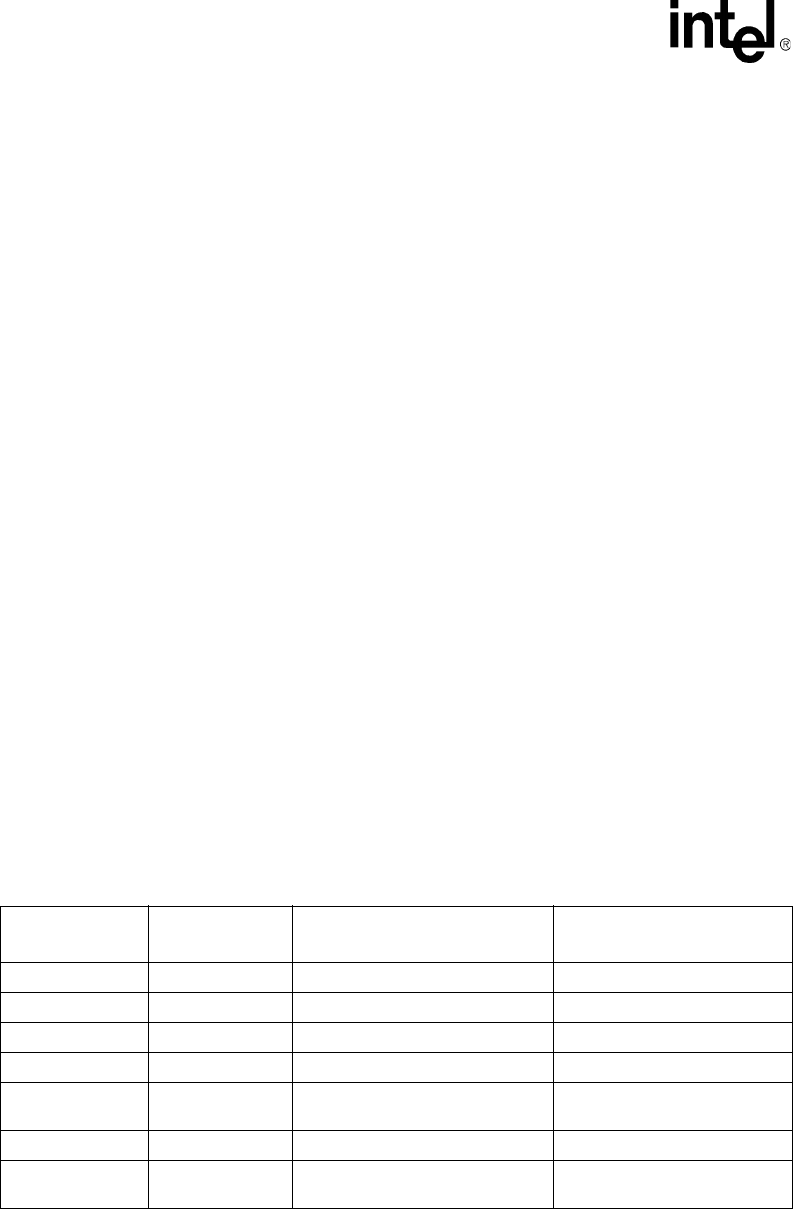

Table 30 provides descriptions for IXF1104 MAC-to-SFP optical module connection signals.

Table 30. Intel

®

IXF1104 MAC-to-SFP Optical Module Interface Connections (Sheet 1 of 2)

IXF1104 MAC

Signal Names

SFP Signal

Names

Description Notes

TX_P_0:3 TD+ Transmit Data, Differential LVDS Output from the IXF1104 MAC

TX_N_0:3 TD- Transmit Data, Differential LVDS Output from the IXF1104 MAC

RX_P_0:3 RD+ Receive Data, Differential LVDS Input to the IXF1104 MAC

RX_N_0:3 RD- Receive Data, Differential LVDS Input to the IXF1104 MAC

I

2

C_CLK MOD-DEF1

I

2

C_CLK output from the

IXF1104 MAC (SCL)

Output from the IXF1104 MAC

I

2

C_DATA_0:3 MOD-DEF2 I

2

C_DATA I/O (SDA) Input/Output

MOD_DEF_0:3 MOD-DEF0

MOD_DEF_0 is TTL Low level

during normal operation.

Input to the IXF1104 MAC