Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet 96

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

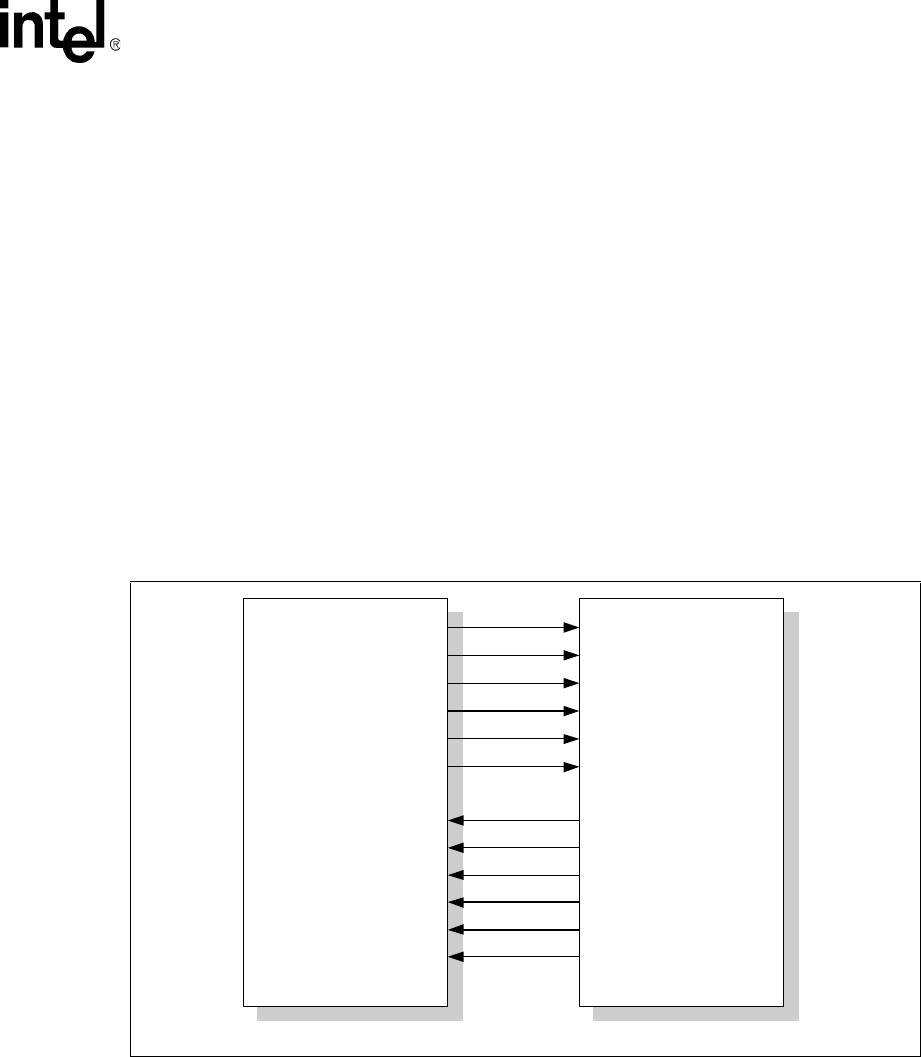

5.4 Reduced Gigabit Media Independent Interface (RGMII)

The IXF1104 MAC supports the RGMII interface standard as defined in the RGMII Version 1.2

specification. The RGMII interface is an alternative to the IEEE 802.3u MII interface.

The RGMII interface is intended as an alternative to the IEEE 802.3u MII and the IEEE 802.3z

GMII. The principle objective of the RGMII is to reduce the number of balls (from a maximum of

28 balls to 12 balls) required to interconnect the MAC and the PHY. This reduction is both cost-

effective and technology-independent. To accomplish this objective, the data paths and all

associated control signals are reduced, control signals are multiplexed together, and both edges of

the clock are used.

• 1000 Mbps operation – clocks operate at 125 MHz

• 100 Mbps operation – clocks operate at 25 MHz

• 10 Mbps operation – clocks operate at 2.5 MHz.

Note: The IXF1104 MAC RGMII interface is multiplexed with signals from the GMII interface. See

Table 16 “Line Side Interface Multiplexed Balls” on page 58 for detailed information.

5.4.1 Multiplexing of Data and Control

Multiplexing of data and control information is achieved by utilizing both edges of the reference

clocks and sending the lower four bits on the rising edge and the upper four bits on the falling edge.

Control signals are multiplexed into a single clock cycle using the same technique. For further

information on timing parameters, see Figure 37 “RGMII Interface Timing” on page 141 and

Table 48 “RGMII Interface Timing Parameters” on page 141.

Figure 18. RGMII Interface

TXC_3:0

TX_CTL_3:0

TXD[3:0]_3

TXD[3:0]_0

TXD[3:0]_1

TXD[3:0]_2

Intel

®

IXF1104

Media Access Controller

TXC_3:0

Quad PHY Device

B3203-0

1

TX_CTL_3:0

TXD[3:0]_3

TXD[3:0]_0

TXD[3:0]_1

TXD[3:0]_2

RXC_3:0

RX_CTL_3:0

RXD[3:0]_3

RXD[3:0]_0

RXD[3:0]_1

RXD[3:0]_2

RXC_3:0

RX_CTL_3:0

RXD[3:0]_3

RXD[3:0]_0

RXD[3:0]_1

RXD[3:0]_2