Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

121 Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

5.9.1 Functional Description

5.9.1.1 Read Access

Read access involves the following:

• Detect assertion of asynchronous Read control signal and latch address

• Generate internal Read strobe

• Drive valid data onto processor bus

• Assert asynchronous Ready signal for required length of time

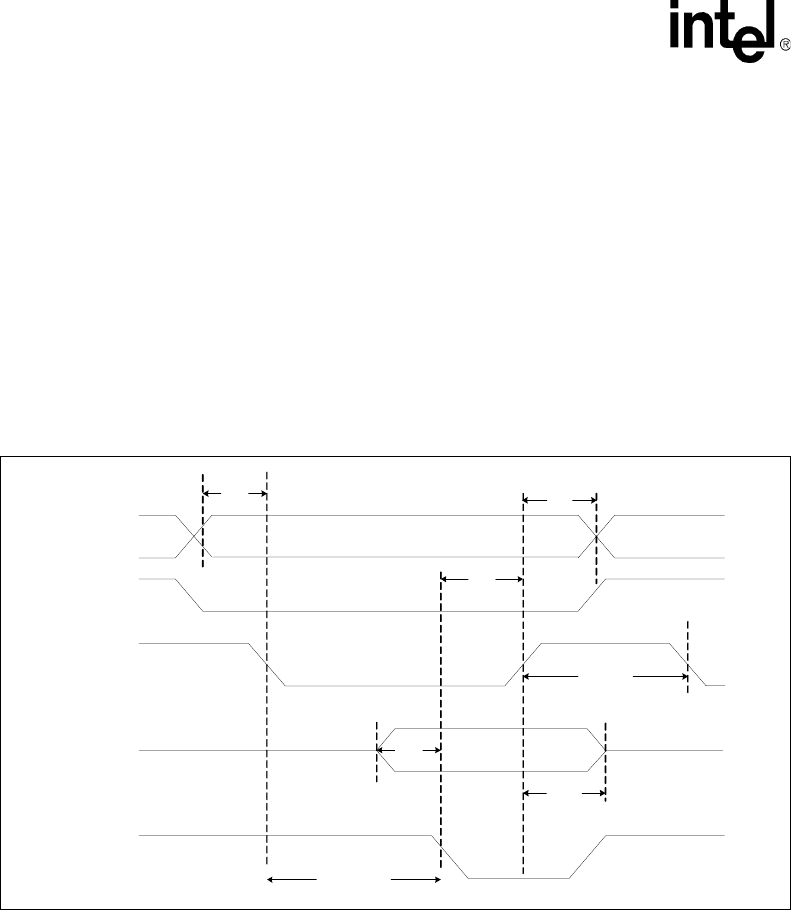

Figure 31 shows the timing of the asynchronous interface for Read access.

5.9.1.2 Write Access

Write process involves the following:

• Detect assertion of asynchronous Write control signal and latch address

• Detect de-assertion of asynchronous Write control signal and latch data

• Generate internal Write strobe

• Assert asynchronous Ready signal for required length of time

Figure 32 shows the timing of the asynchronous interface for Write accesses.

Figure 31. Read Timing Diagram - Asynchronous Interface

T

CAS

T

CAH

T

CRR

T

CDRS

T

CDRH

T

CDRD

T

CRH

u

Px_ADD[10:0]

uPx_RdN

uPx_CsN

u

Px_Data[31:0]

uPx_RdyN

B5103-01