Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

173 Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

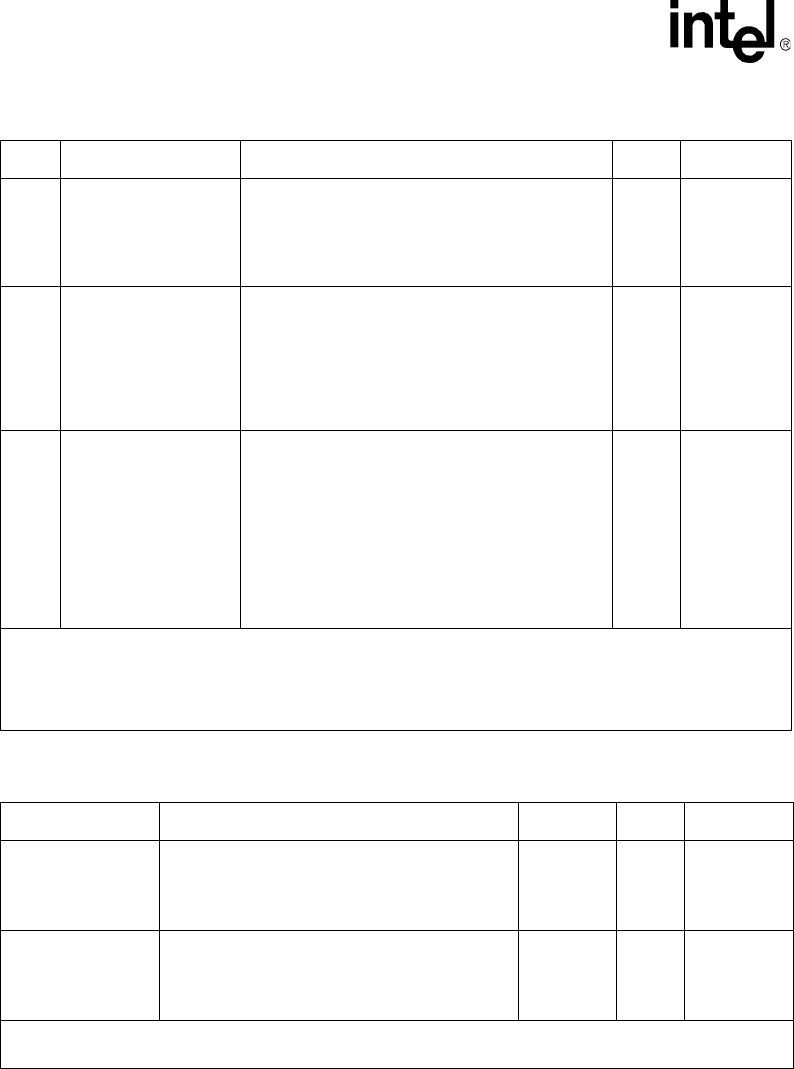

2 B/Cast Drop En

This bit enables a Global filter on broadcast

frames.

0 = All broadcast frames are passed to the SPI3

Interface.

1 = All broadcast frames are dropped.

2

R/W 0

1 M/Cast Match En

This bit enables a filter on multicast frames.

0 = All muticast frames are good and passed to

the SPI3 Interface.

1 = Only multicast frames with a destination

address that matches the

PortMulticastAddress are forwarded. All other

muticast frames are dropped.

2

R/W 0

0 U/Cast Match En

2

This bit enables a filter on unicast frames.

0 = All unicast frames are good and are passed

to the SPI3 Interface.

1 = Only unicast frames with a Destination

Address that matches the Station Address

are forwarded. All other unicast frames are

dropped.

2

NOTE: The VLAN filter overrides the unicast filter.

Therefore, a VLAN frame cannot be

filtered based on the unicast address.

R/W 0

Table 92. Port Multicast Address ($ Port_Index +0x1A – +0x1B)

Name Description Address Type

*

Default

Port Multicast

Address Low

This address compares against multicast frames

at the receiving side if multicast filtering is

enabled.

This register contains bits 31:0 of the address.

Port_Index

+ 0x1A

R/W 0x0000000

Port Multicast

Address High

This address compares against multicast frames

at the receiving side if Multicast filtering is

enabled.

This register contains bits 47:32 of the address.

Port_Index

+ 0x1B

R/W 0x00000000

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No clear;

R/W/C = Read/Write, Clear on Write

Table 91. RX Packet Filter Control ($ Port_Index + 0x19) (Sheet 2 of 2)

Bit Name Description Type

1

Default

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

2. Used in conjunction with the “RX FIFO Errored Frame Drop Enable ($0x59F)” on page 196. This allows the

frame to be dropped in the RX FIFO. Otherwise, the frame is sent out the SP3 interface and may be

optionally signaled with an RERR (see bit 0 of “SPI3 Receive Configuration ($0x701)”.