Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

213 Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

8.4.9 SPI3 Register Overview

Table 146 through Table 148 “Address Parity Error Packet Drop Counter ($0x70A)” on page 219

provide an overview of the SPI3 registers.

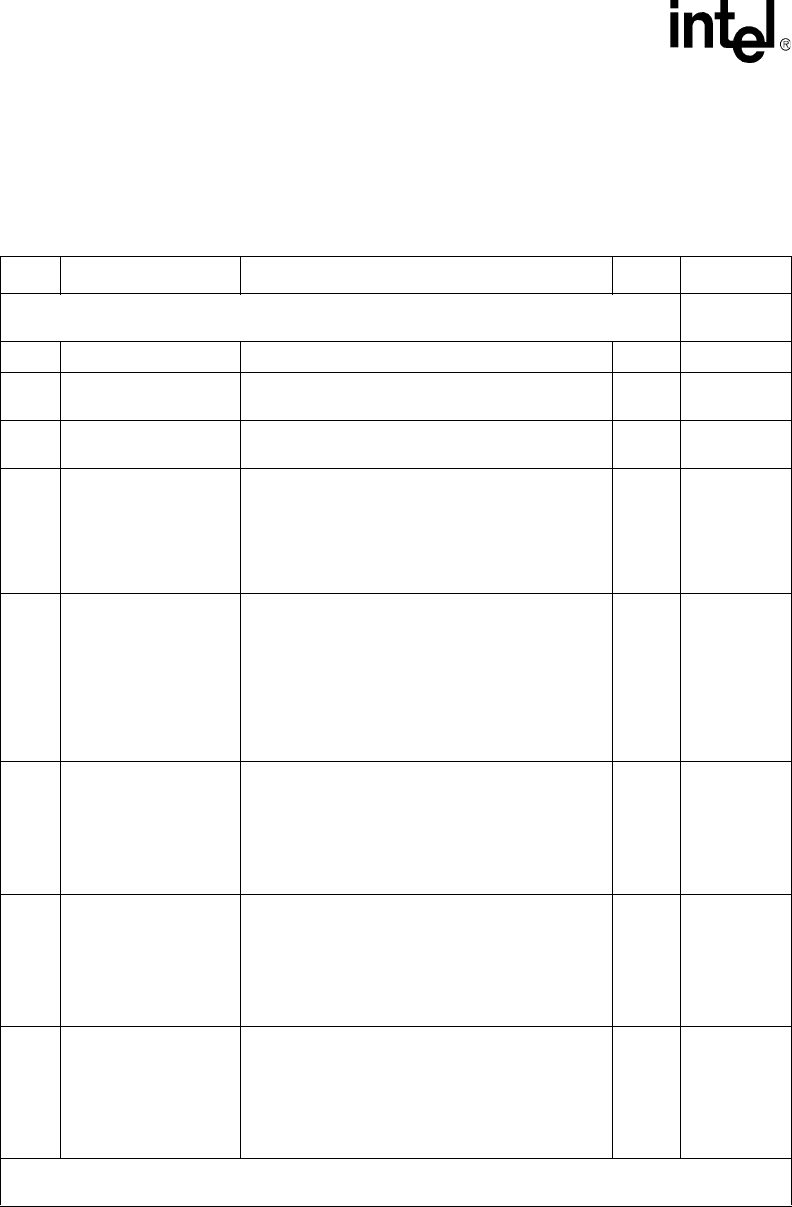

Table 146. SPI3 Transmit and Global Configuration ($0x700) (Sheet 1 of 3)

Bit Name Description Type

1

Default

Register Description:

This register gives the configuration related to the SPI3 Transmitter

and Global configuration (4 x 8 mode).

0x00200000

31:24 Reserved Reserved RO 0x00

23

SPI3 Transmitter Soft

Reset

1 = The SPI3 TX block is reset. R/W 0

22

SPI3 Receiver Soft

Reset

1 = The SPI3 RX block is reset. R/W 0

21 SPHY/MPHY Mode

0 = Indicates that SPI3 block operates in 32-bit

MPHY mode.

1 = Indicates that the SPI3 block operates in 4 x 8

SPHY mode.

This configuration affects both the SPI3 transmitter

and receiver functionality.

R/W 1

20 Tx_ad_prtyer_drop

Indicates whether to drop packets received with

parity error during the address selection phase

(Tsx and nTenb High) should be dropped.

0 = Do not drop packets with address parity error

1 = Drop packets with address parity error

This is applicable only in MPHY mode of

operation. This bit is ignored in SPHY (4 x 8) mode

as there will be no address selection.

R/W 0

19 Dat_prtyer_drp Port 3

SPHY/MPHY Mode:

Indicates whether to drop packets with data parity

error for port 3.

0 = Do not drop packets with data parity error

(default)

1 = Drop packets with data parity error

R/W 0x0

18 Dat_prtyer_drp Port 2

SPHY/MPHY Mode:

Indicates whether to drop packets with data parity

error for port 2.

0 = Do not drop packets with data parity error

(default)

1 = Drop packets with data parity error

R/W 0

17 Dat_prtyer_drp Port 1

SPHY/MPHY Mode:

Indicates whether to drop packets with data parity

error for port 1.

0 = Do not drop packets with data parity error

(default)

1 = Drop packets with data parity error

R/W 0

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write