Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

181 Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

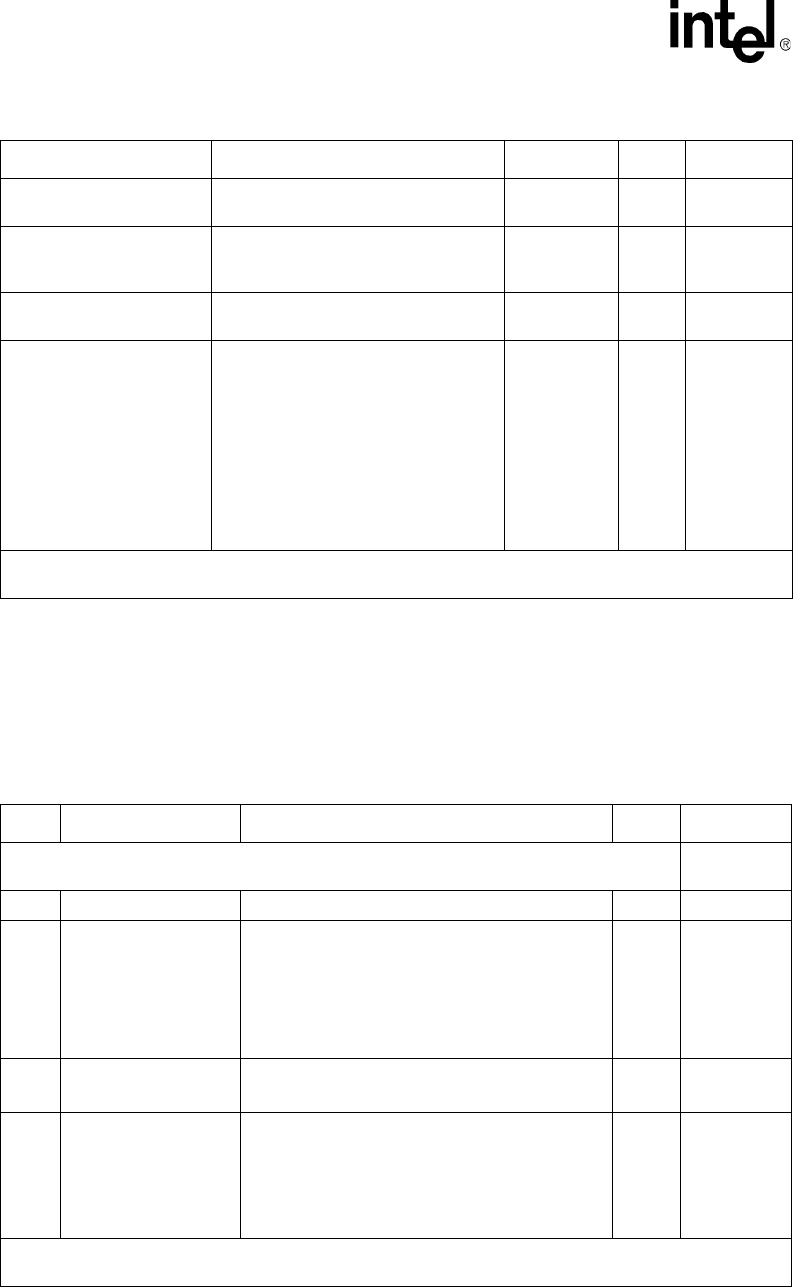

8.4.4 PHY Autoscan Registers

Note: These register hold the current values of the PHY registers only when Autoscan (see Section 5.5.8,

“Autoscan Operation” on page 103) is enabled and the IXF1104 MAC is configured in copper

mode. These registers are not applicable in fiber mode.

TxTagged

Number of OK frames with VLAN tag.

(Type field = 0x8100).

Port_Index +

0x55

R 0x00000000

TxCRCError

Number of frames transmitted with a

legal size but with the wrong CRC field

(also called FCS field).

Port_Index +

0x56

R 0x00000000

TxPauseFrames

Number of pause MAC frames

transmitted.

Port_Index +

0x57

R 0x00000000

TxFlowControlCollisions

Send

Intentionally generates collisions to

curb reception of incoming traffic due to

insufficient memory available for

additional frames. The port must be in

half-duplex mode with flow control

enabled.

NOTE: To receive a correct statistic, a

last frame may have to be

transmitted after the last flow

control collisions send.

NOTE: NA - half-duplex only

Port_Index +

0x58

R 0x00000000

Table 95. PHY Control ($ Port Index + 0x60) (Sheet 1 of 2)

Bit Name Description Type

1

Default

0x00000010

001000

31:16 Reserved Reserved RO 0x0000

15 Reset

PHY Soft Reset. Resets the PHY registers to their

default value.

This register bit self-clears after the reset is

complete.

0 = Normal Operation

1 = PHY reset

RO 0

14 Loopback

0 = Disable loopback mode

1 = Enable loopback mode

RO 0

13 Speed Selection

0.6 (Speed<1> 0.13 (Speed<0>)

00 =10 Mbps

01 =100 Mbps

10 =1000 Mbps (manual mode not allowed)

11 = Reserved

RO 0

2

1. RO = Read Only; RR = Clear on Read; W = Write; R/W = Read/Write

2. This register is ignored if auto-negotiation is enabled.

Table 94. MAC TX Statistics ($ Port_Index +0x40 – +0x58) (Sheet 4 of 4)

Name Description Address Type

1

Default

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write