Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet 52

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

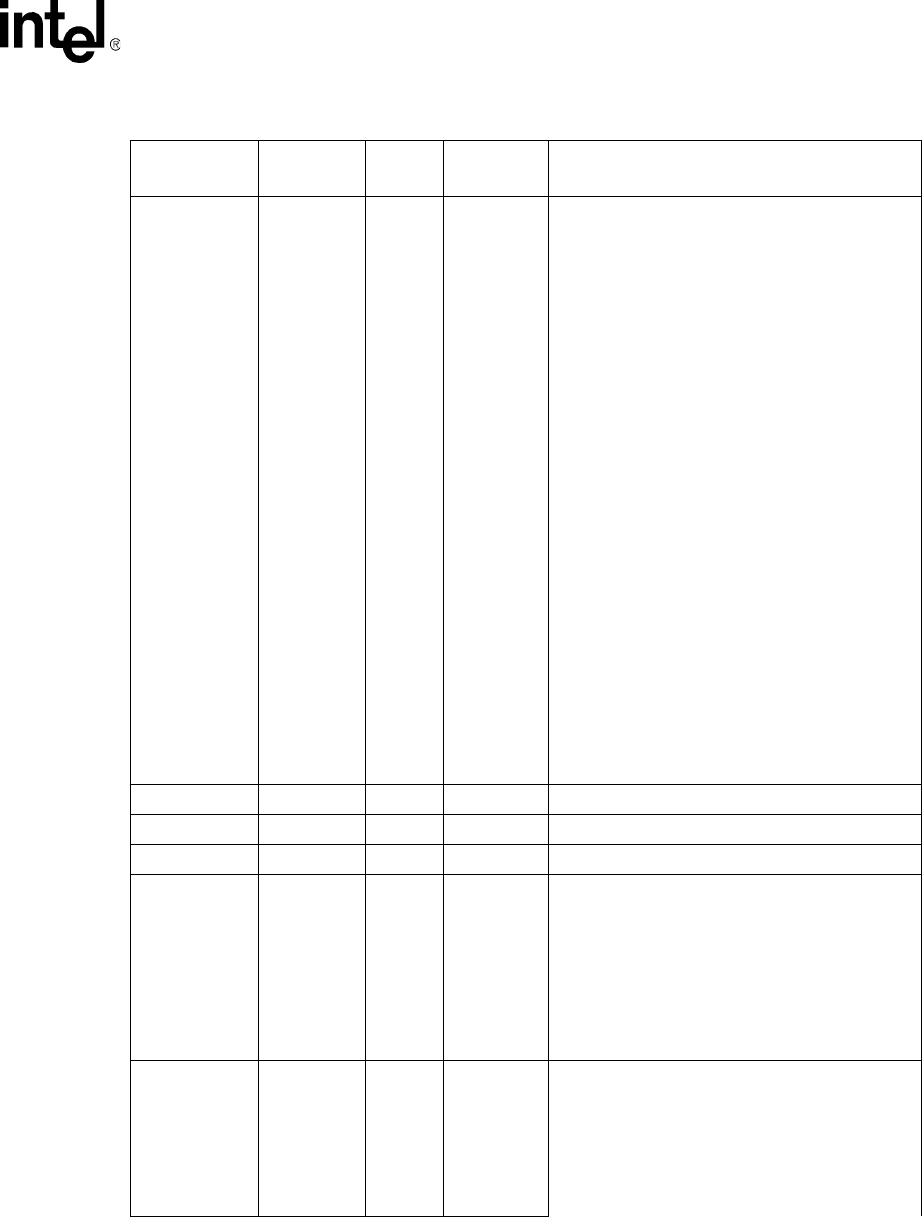

UPX_DATA31

UPX_DATA30

UPX_DATA29

UPX_DATA28

UPX_DATA27

UPX_DATA26

UPX_DATA25

UPX_DATA24

UPX_DATA23

UPX_DATA22

UPX_DATA21

UPX_DATA20

UPX_DATA19

UPX_DATA18

UPX_DATA17

UPX_DATA16

UPX_DATA15

UPX_DATA14

UPX_DATA13

UPX_DATA12

UPX_DATA11

UPX_DATA10

UPX_DATA9

UPX_DATA8

UPX_DATA7

UPX_DATA6

UPX_DATA5

UPX_DATA4

UPX_DATA3

UPX_DATA2

UPX_DATA1

UPX_DATA0

L17

J17

H16

J16

M15

N15

K15

H14

K13

G12

K12

G11

H11

G10

K10

M10

N10

J9

H9

L8

N7

L7

L6

P5

K5

M5

N5

L4

M3

L3

K3

L2

Input/

Output

3.3 V LVTTL

Data bus.

32-bit mode: Uses [31:0]

16-bit mode: Uses [15:0]

8-bit mode: Uses [7:0]

UPX_CS_L R3 Input 3.3 V LVTTL Chip Select. Active Low.

UPX_WR_L T4 Input 3.3 V LVTTL Write Strobe. Active Low.

UPX_RD_L V6 Input 3.3 V LVTTL Read Strobe. Active Low.

UPX_RDY_L M1

Open

Drain

Output*

3.3 V LVTTL

Cycle complete indicator.

Active Low.

NOTE: An external pull-up resistor is required for

proper operation.

NOTE: *Dual-mode I/O

Normal operation: Open drain output

Boundary Scan Mode: Standard CMOS

output

UPX_WIDTH1

UPX_WIDTH0

T5

U16

Input 3.3 V LVTTL

Data bus width select.

UPX_WIDTH[1:0] specifies the CPU bus width.

UPX_WIDTH[1:0]

00

01

1x

Mode

8-bit

16-bit

32-bit

Table 7. CPU Interface Signal Descriptions (Sheet 2 of 2)

Signal Name

Ball

Designator

Type Standard Description