Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet 38

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

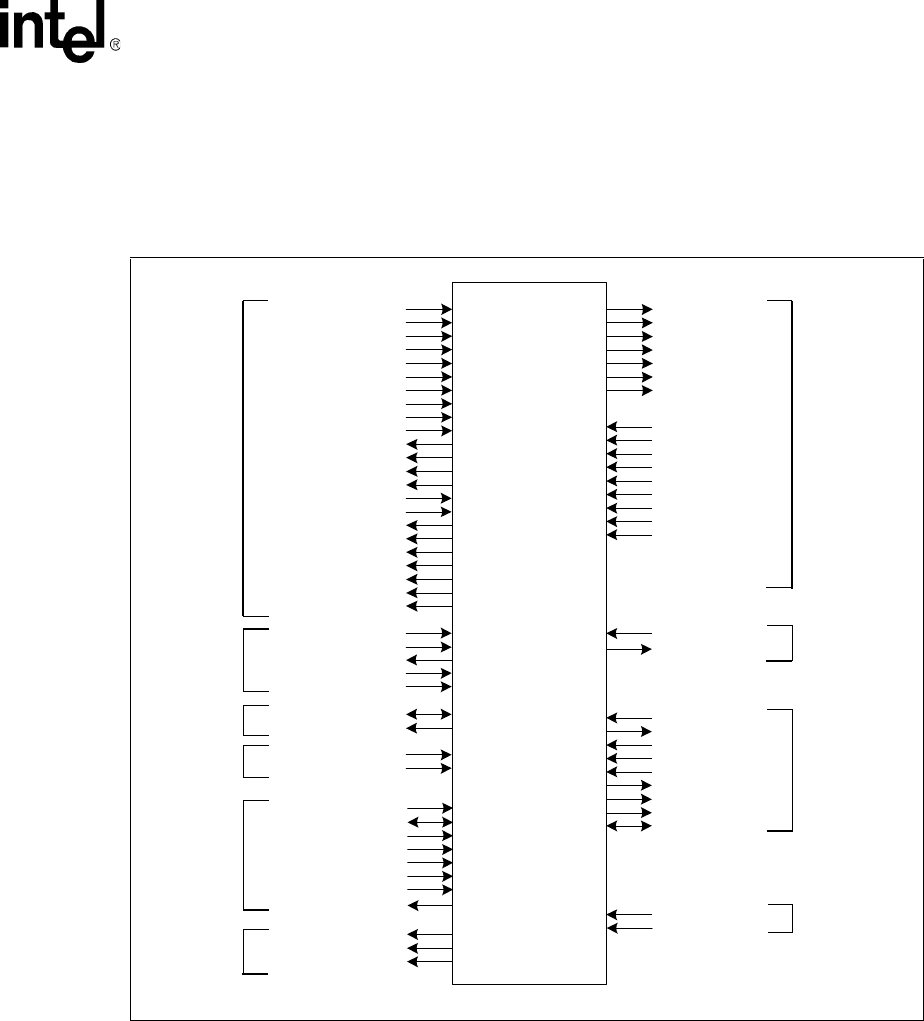

4.2 Interface Signal Groups

This section describes the IXF1104 MAC signals in groups according to the associated interface or

function. Figure 4 shows the various interfaces available on the IXF1104 MAC.

Figure 4. Interface Signals

T DAT[ 31:0]

TFCLK

TENB_0

TERR_0

TPRTY_0

TMOD[1:0]

TSX

TSOP_0

TEOP_0

TADR[1:0]

DTPA_0:3

STPA

PTPA

R D AT[ 31: 0]

RFCLK

RENB_0

RVAL_0

RERR_0

RPRTY_0

RMOD[1:0]

RSX

RSOP_0

REOP_0

TMS

TDI

TDO

TCLK

MDIO

MDC

TXPAUSEADD[2:0]

TXPAUSEFR

UPX_WIDTH[1:0]

U PX_D AT A[ 31:0]

UPX_ADD[10:0]

UPX_BADD[1:0]

UPX_WR_L

UPX_RD_L

UPX_CS_L

UPX_RDY_L

LED_CLK

LED_DATA

LED _LAT CH

SYS_RES_L

CLK125

MOD _DEF_0:3

TX_DISABLE_0:3

TX_F AU LT_0:3

R X_LOS _0:3

TX_F AU LT_IN T

R X_LOS _IN T

MOD _DEF_INT

I

2

C_CLK

I

2

C_DATA_0:3

SPI3

Interface

JTA G

Interface

MDIO

Interface

Pause

Control

Interface

CPU

Interface

LED

Interface

System

In terface

GMII RGMII

GMII and

RGMII

In terfaces*

* Data and clock balls are shared for

GMII and RGMII Interfaces

SerDes

In terface

Optical

Module

In terface

Si gn als*

*

** These optical module signals

are multiplexed on the GMII balls.

RX_P/N_0:3

TX_P/N_0:3

TRST_L

Intel

®

IXF1104

Media Access

Controller

B3181-01

MPHYSPH Y

TFCLK

TEN B_0: 3

TER R _0: 3

T PR TY_0: 3

TSO P_0: 3

TEO P_0: 3

TDAT[7:0]_0:3

TADR[1:0]

D TPA_0: 3

PTPA

RDAT[7:0]_0:3

RFCLK

RENB_0:3

R VAL_0: 3

RERR_0:3

RPRTY_0:3

R SO P_0: 3

R EO P_0: 3

TXC_0:3

TXD [ 7:0] _3

T XC _0: 3

TD[3:0]_3

TXD [ 7:0] _2 T D[ 3:0] _2

TXD [ 7:0] _1 T D[ 3:0] _1

TXD [ 7:0] _0

TD[3:0]_0

TX_EN_0:3

TX_ER_0:3

T X_C TL_0: 3

R XC _0:3 R XC _0: 3

RXD[7:0]_3

RD[3:0]_3

RXD[7:0]_2

RD[3:0]_2RXD[7:0]_1

RD[3:0]_1

RXD[7:0]_0

RD[3:0]_0

R X_DV_0:3

RX_ER_0:3

CRS_0:3

C OL_0:3

R X_C TL_0: 3