Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

215 Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

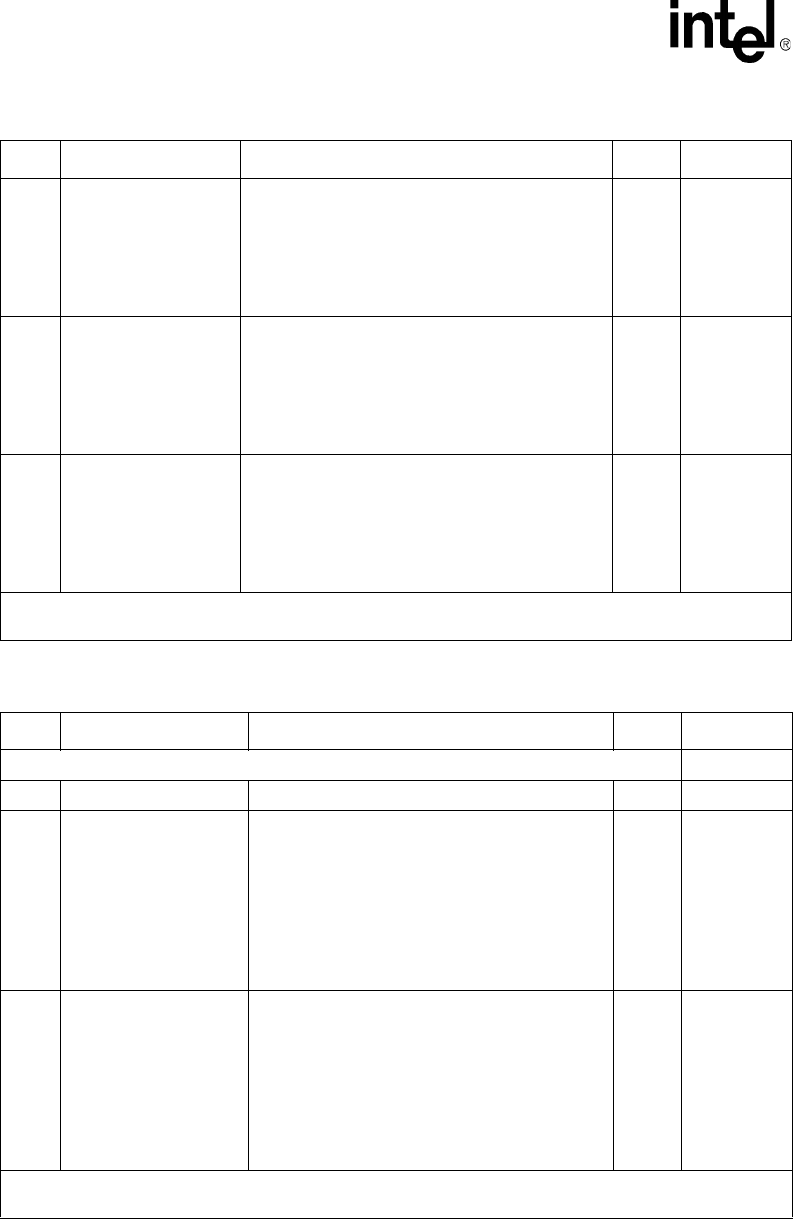

2 Tx_port_enable Port 2

SPHY Mode:

0 = Disables the selected SPI3 TX port 2

1 = Enables the selected SPI3 TX port 2

MPHY Mode:

0 = Disables the selected SPI3 TX port 2

1 = Enables the selected SPI3 TX port 2

R/W 1

1 Tx_port_enable Port 1

SPHY Mode:

0 = Disables the selected SPI3 TX port 1

1 = Enables the selected SPI3 TX port 1

MPHY Mode:

0 = Disables the selected SPI3 TX port 1

1 = Enables the selected SPI3 TX port 1

R/W 1

0 Tx_port_enable Port 0

SPHY Mode:

0 = Disables the selected SPI3 TX port 0

1 = Enables the selected SPI3 TX port 0

MPHY Mode:

0 = Disables the selected SPI3 TX port 0

1 = Enables the selected SPI3 TX port 0

R/W 1

Table 147. SPI3 Receive Configuration ($0x701) (Sheet 1 of 4)

Bit Name Description Type

1

Default

Register Description:

This register gives the configuration related to the SPI3 receiver. 0x00000F80

31:28 Reserved Reserved RO 0x0

27 B2B_PAUSE Port 3

SPHY Mode:

Indicates the number of pause cycles to be

introduced between back-to-back transfers for

port 3.

0 = Zero pause cycles

1 = Two pause cycles

MPHY Mode:

NA

R/W 0

26 B2B_PAUSE Port 2

SPHY Mode:

Indicates the number of pause cycles to be

introduced between back-to-back transfers for

port 2.

0 = Zero pause cycles

1 = Two pause cycles

MPHY Mode:

NA

R/W 0

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

Table 146. SPI3 Transmit and Global Configuration ($0x700) (Sheet 3 of 3)

Bit Name Description Type

1

Default

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write