Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

97 Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

5.4.2 Timing Specifics

The IXF1104 MAC RGMII complies with RGMII Rev1.2a requirements. Table 27 provides the

timing specifics.

5.4.3 TX_ER and RX_ER Coding

To reduce interface power, the transmit error condition (TX_ER) and the receive error condition

(RX_ER) are encoded on the RGMII interface to minimize transitions during normal network

operation (refer to Table 28 on page 97 for the encoding method). Table 27 provides signal

definitions for RGMII.

The value of RGMII_TX_ER and RGMII_TX_EN are valid at the rising edge of the clock while

TX_ER is presented on the falling edge of the clock. RX_ER coding behaves in the same way (see

Table 28, Figure 19, and Figure 20).

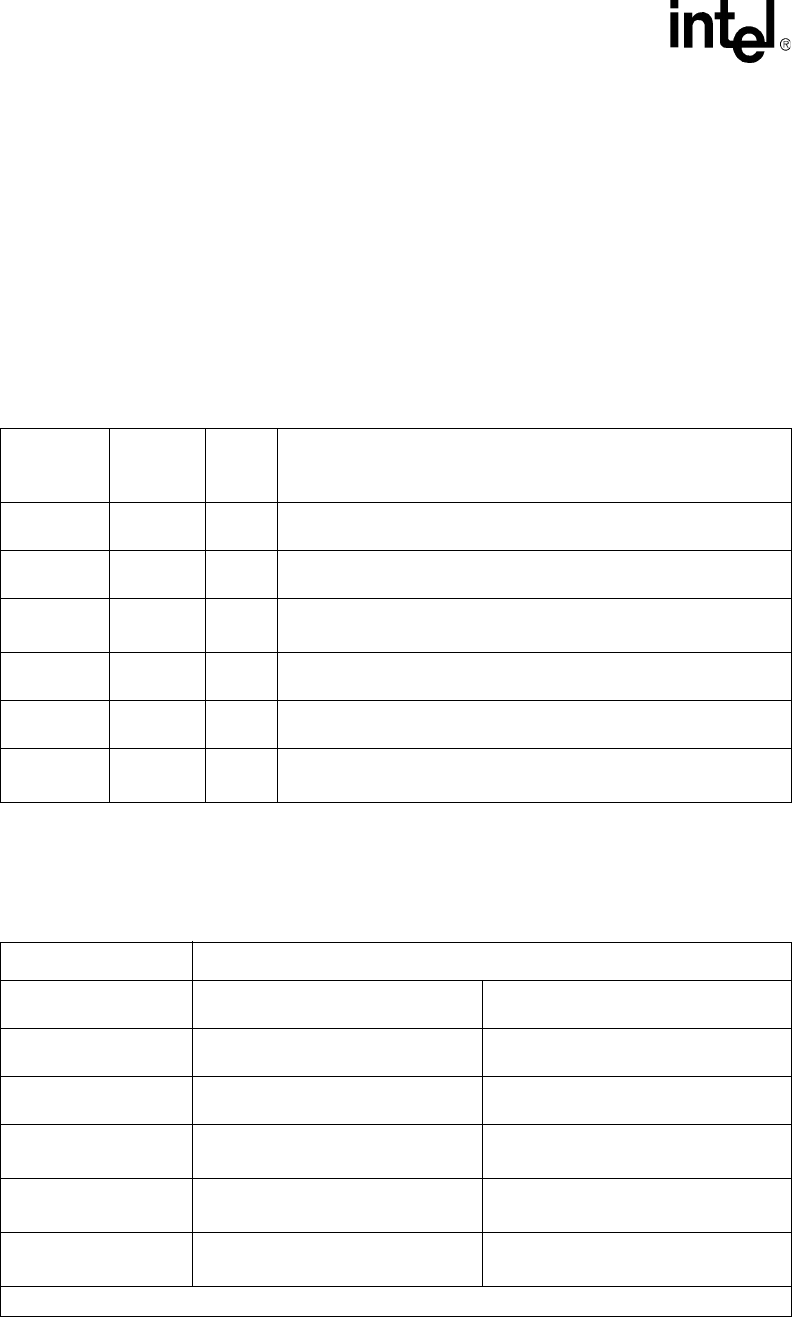

Table 27. RGMII Signal Definitions

IXF1104

MAC Signal

RGMII

Standard

Signal

Source Description

TXC_0:3 TXC MAC

Depending on speed, the transmit reference clock is 125 MHz, 25

MHz, or 2.5 MHz +/– 50ppm.

TD[3:0]_n TD<3:0> MAC

Contains register bits 3:0 on the rising edge of TXC and register bits

7:4 on the falling edge of TXC.

TX_EN TX_CTL MAC

TXEN is on the leading edge of TXC.

TX_EN xor TX_ER is on the falling edge of TXC.

RXC_0:3 RXC PHY

Continuous reference clock is 125 MHz, 25 MHz, or 2.5 MHz +/– 50

ppm.

RD[3:0]_n RD<3:0> PHY

Contains register bits 3:0 on the leading edge of RXC and register bits

7:4 on the trailing edge of RXC.

RX_DV RX_CTL PHY

RX_DV is on the leading edge of RXC.

RX_DV or RXERR is the falling edge of RXC.

Table 28. TX_ER and RX_ER Coding Description

Condition Description

Receiving valid frame,

no errors

RX_DV = true

Logic High on rising edge of RXC

RX_ER = false

Logic High on the falling edge of RXC

Receiving valid frame,

with errors

RX_DV = true

Logic High on rising edge of RXC

RX_ER = true

Logic Low on the falling edge of RXC

Receiving invalid frame

(or no frame)

RX_DV = false

Logic Low on rising edge of RXC

RX_ER = false

Logic Low on the falling edge of RXC

Transmitting valid frame,

no errors

TX_EN = true

Logic High on rising edge of TXC

TX_ER =false

Logic High on the falling edge of TXC

Transmitting valid frame

with errors

TX_EN = true

Logic High on rising edge of TXC

TX_ER = true

Logic Low on the falling edge of TXC

Transmitting invalid

frame (or no frame)

TX_EN = false

Logic Low on rising edge of TXC

TX_ER = false

Logic low on the falling edge of TXC

NOTE: Refer to Figure 19 for TX_CTL behavior, and Figure 20 for RX_CTL behavior.