Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet 76

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

5.1.4 Fiber Mode

When the IXF1104 MAC is configured for fiber mode, the TX Data path from the MAC is an

internal

10-bit interface as described in the IEEE 802.3z specification. It is connected directly to an internal

SerDes block for serialization/deserialization and transmission/reception on the fiber medium to

and from the link partner.

The MAC contains all of the PCS (8B/10B encoding and 10B/8B decoding) required to encode and

decode the data. The MAC also supports auto-negotiation per the IEEE 802.3z specification via

access to the “TX Config Word ($ Port_Index + 0x17)", “RX Config Word ($ Port_Index + 0x16)",

and “Diverse Config Write ($ Port_Index + 0x18)".

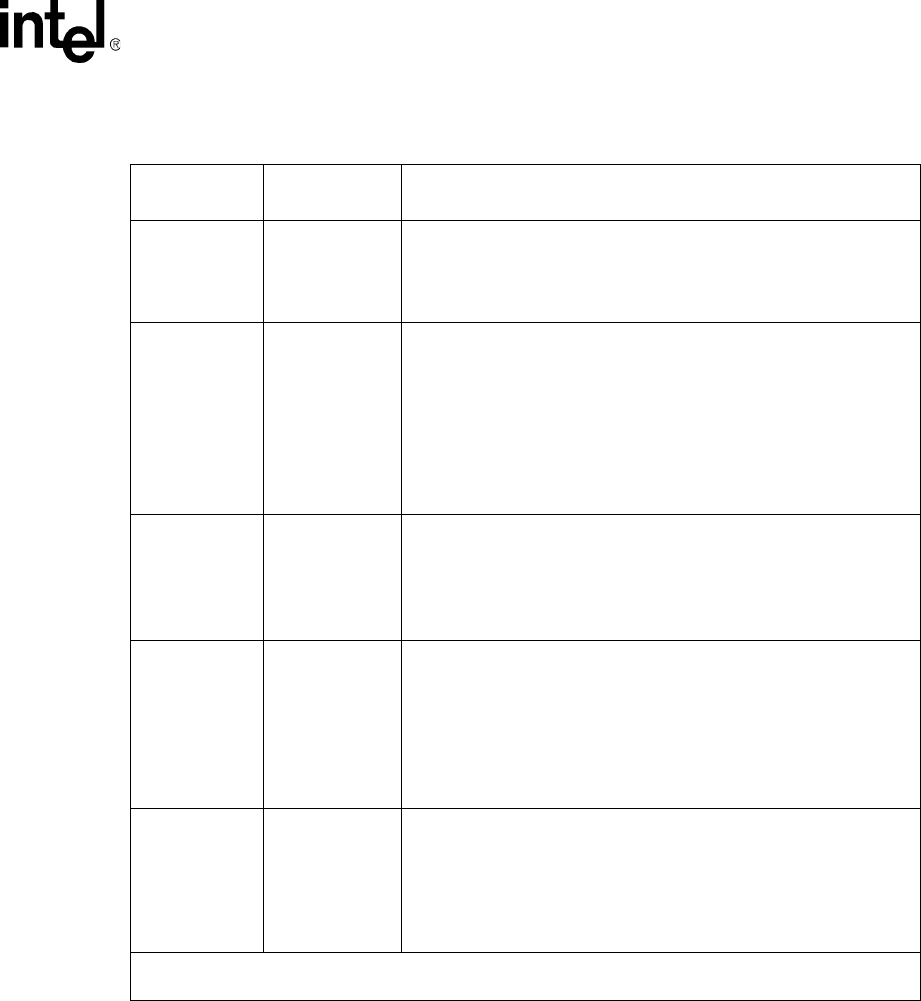

Table 24. Operational Mode Configuration Registers

Register Name

Register

Address

Description

“Desired Duplex

($ Port_Index +

0x02)"

0x002 – Port 0

0x082 – Port 1

0x102 – Port 2

0x182 – Port 3

The “Desired Duplex ($ Port_Index + 0x02)” on page 163 defines

whether a port is to be configured for full-duplex or half-duplex

operation.

NOTE: Half-duplex operation is only valid for 10/100 speeds where the

RGMII line interface has been selected.

“MAC IF Mode

and RGMII

Speed ($

Port_Index +

0x10)"

0x010 – Port 0

0x090 – Port 1

0x110 – Port 2

0x190 – Port 3

The “MAC IF Mode and RGMII Speed ($ Port_Index + 0x10)” on

page 167 determines the MAC operational frequency and mode for a

given port.

NOTE: Set the “Clock and Interface Mode Change Enable Ports 0 - 3

($0x794)” on page 221 to 0x0 prior to any change in the

register value. This ensures that a change in the MAC clock

frequency is controlled correctly. If the “Clock and Interface

Mode Change Enable Ports 0 - 3 ($0x794)" is not used

correctly, the IXF1104 MAC may not be configured to the

proper mode.

“Port Enable

($0x500)"

0x500

Bit 0 – Port 0

Bit 1 – Port 1

Bit 2 – Port 2

Bit 3 – Port 3

Each “Port Enable ($0x500)" bit relates to a port. Set the appropriate bit

to 0x1 to enable a port. This should be the last step in the configuration

process for a port.

“Interface Mode

($0x501)"

0x501

Bit 0 – Port 0

Bit 1 – Port 1

Bit 2 – Port 2

Bit 3 – Port 3

The “Interface Mode ($0x501)" selects whether a port operates with a

copper (RGMII or GMII) line-side interface an integrated SerDes fiber

line-side interface.

For copper operation for a given port, set the relevant bit to 0x1.

For fiber operation for a given port, set the relevant bit to 0x0.

NOTE: All ports are configured for fiber operation in the IXF1104 MAC

default mode of operation.

“Clock and

Interface Mode

Change Enable

Ports 0 - 3

($0x794)"

0x794

Bit 0 – Port 0

Bit 1 – Port 1

Bit 2 – Port 2

Bit 3 – Port 3

The “Clock and Interface Mode Change Enable Ports 0 - 3 ($0x794)"

indicates to an internal clock generator when to sample the new value

of the “MAC IF Mode and RGMII Speed ($ Port_Index + 0x10)" and the

“Interface Mode ($0x501)" (copper/fiber).

When any of these two configuration values are changed for a port, the

corresponding bits must be kept in this register under reset by writing

0x0 to the relevant bit.

NOTE: The initialization sequence provided in Section 6.1, “Change Port Mode Initialization Sequence” on

page 130 must be followed for proper configuration of the IXF1104 MAC.