Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet 108

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

5.7.2 Functional Descriptions

5.7.2.1 High-Speed Serial Interface

These signals are responsible for transfer of the actual data at 1.25 Gbps. Table 41 “DC

Specifications” on page 134 shows the data is 8B/10B encoded and transmitted differentially.

The following signals are required to implement the high-speed serial interface:

• TX_P_0:3

• TX_N_0:3

• RX_P_0:3

• RX_N_0:3

5.7.2.2 Low-Speed Status Signaling Interface

The following Low-Speed signals indicate the state of the line through the Optical Module

Interface:

• MOD_DEF_0:3

• TX_FAULT_0:3

• RX_LOS_0:3

• TX_DISABLE_0:3

• MOD_DEF_INT

• TX_FAULT_INT

• RX_LOS_INT

5.7.2.2.1 MOD_DEF_0:3

MOD_DEF_0:3 are direct inputs to the IXF1104 MAC and are pulled to a logic Low level during

normal operation, indicating that a module is present for each channel respectively. If a module is

not present, a logic High is received, which is achieved by an external pull-up resistor at the

IXF1104 MAC device pad.

The status of each bit (one for each port) is found in bits [3:0] of the “Optical Module Status Ports

0-3 ($0x799)” on page 222). Any change in the state of these bits causes a logic Low level on the

MOD_DEF_INT output if this operation is enabled.

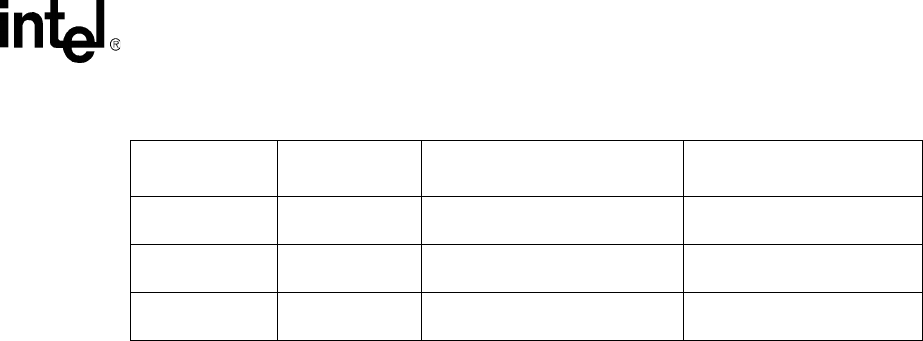

TX_DISABLE_0:3 TX DISABLE

Transmitter disable, logic High,

open collector compatible

Output from the IXF1104 MAC

TX_FAULT_0:3 TX FAULT

Transmitter fault, logic High, open

collector compatible

Input to the IXF1104 MAC

RX_LOS_0:3 LOS

Receiver loss-of-signal, logic High,

open collector compatible

Input to the IXF1104 MAC

Table 30. Intel

®

IXF1104 MAC-to-SFP Optical Module Interface Connections (Sheet 2 of 2)

IXF1104 MAC

Signal Names

SFP Signal

Names

Description Notes