Cavium Processor Complex: PCI

ATCA-9305 User’s Manual 10009109-01

3-2

The CN5860 and switch route packets using SPI-4.2 and control information flow using PCI.

The CN5860 has two SPI-4.2 interfaces with each one supporting up to 16 ports. Two high-

speed SPI-4.2 Altera (Stratix™ GX) FPGAs function as the SPI-to-XAUI bridge for each pro-

cessor to switch complex. The PCI interface supports up to four ports, consequently a total

of 36 ports can be supported internally by each CN5860.

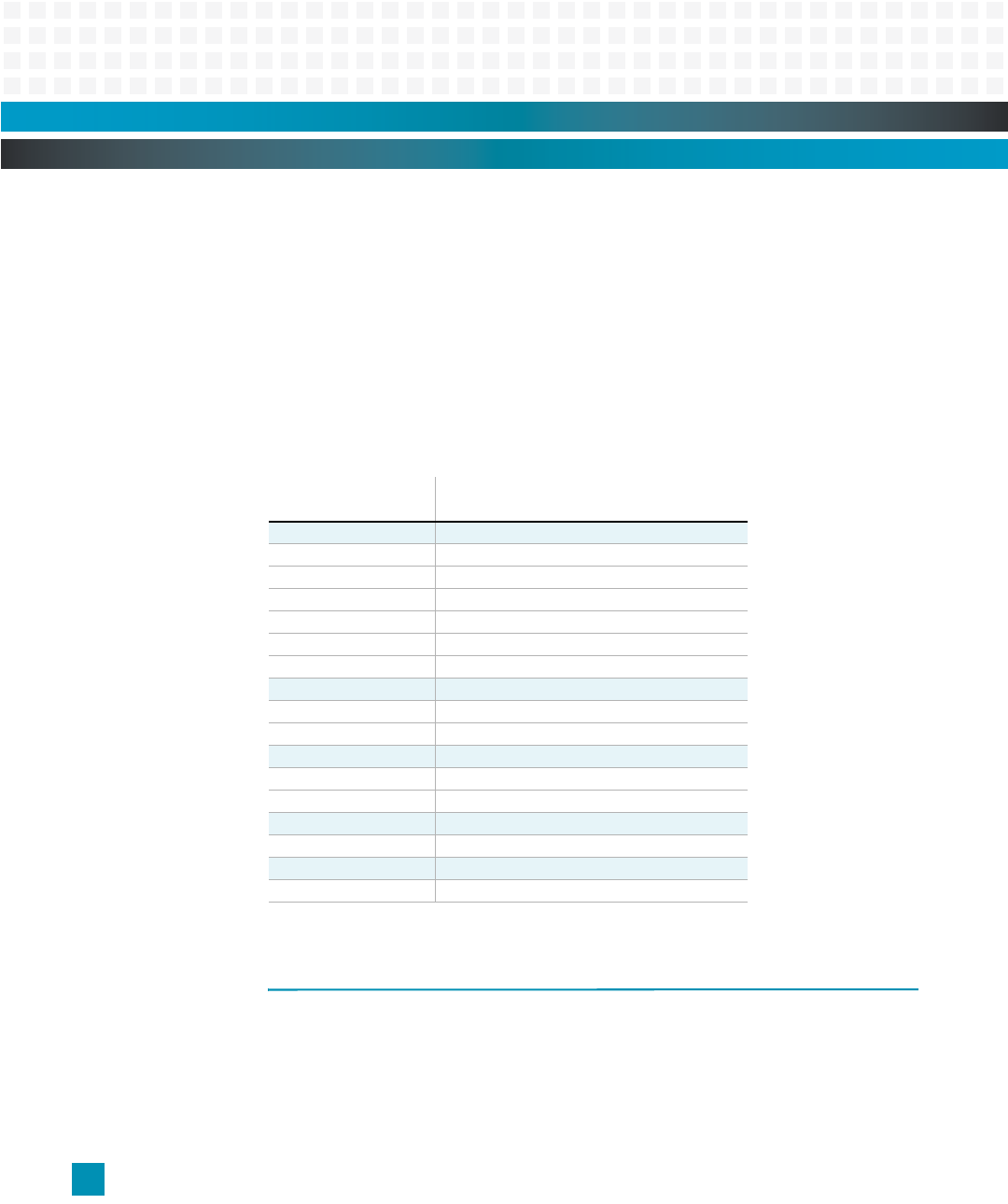

Cavium Memory Map

Although the Cavium processors are 64-bit, the ATCA-9305 uses a 49-bit implementation.

Refer to the Cavium Networks OCTEON Plus CN58xx Hardware Reference Manual for more

detailed information on the memory map.

Table 3-2: Cavium Address Summary

PCI

The Cavium is a slave device on the PCI bus. The Cavium U-boot monitor image is provided

by the MPC8548 management processor via PCI. The MPC8548 monitors the Cavium boot

status and has the ability to try alternate boot images if the current one fails.

Hex Physical

Address: Register Description:

1,2000,0000,0000 reserved

1,1F00,0000,0000 Cavium Hardware registers

1,1E00,0000,0000 PCI Memory Space (6)

1,1D00,0000,0000 PCI Memory Space (5)

1,1C00,0000,0000 PCI Memory Space (4)

1,1B00,0000,0000 PCI Memory Space (3)

1,1A00,0000,0000 PCI I/O Space

1,1910,0000,0000 reserved

1,1900,0000,0000 PCI Special Space

1,0700,0000,0000 CN58xx Registers

1,0001,0000,0000 reserved

1,0000,0000,0000 Local Boot Bus

0,0004,1000,0000 DDR2 SDRAM, middle block (256-512 MB)

0,0004,0000,0000 reserved

0,0000,2000,0000 DDR2 SDRAM, upper block (512 MB-2 GB)

1

1. This depends on how much memory is installed.

0,0000,1000,0000 reserved

0,0000,0000,0000 DDR2 SDRAM, bottom block (256 MB)