Management Processor CPLD: MPC8548 PLD Register

10009109-01 ATCA-9305 User’s Manual

5-11

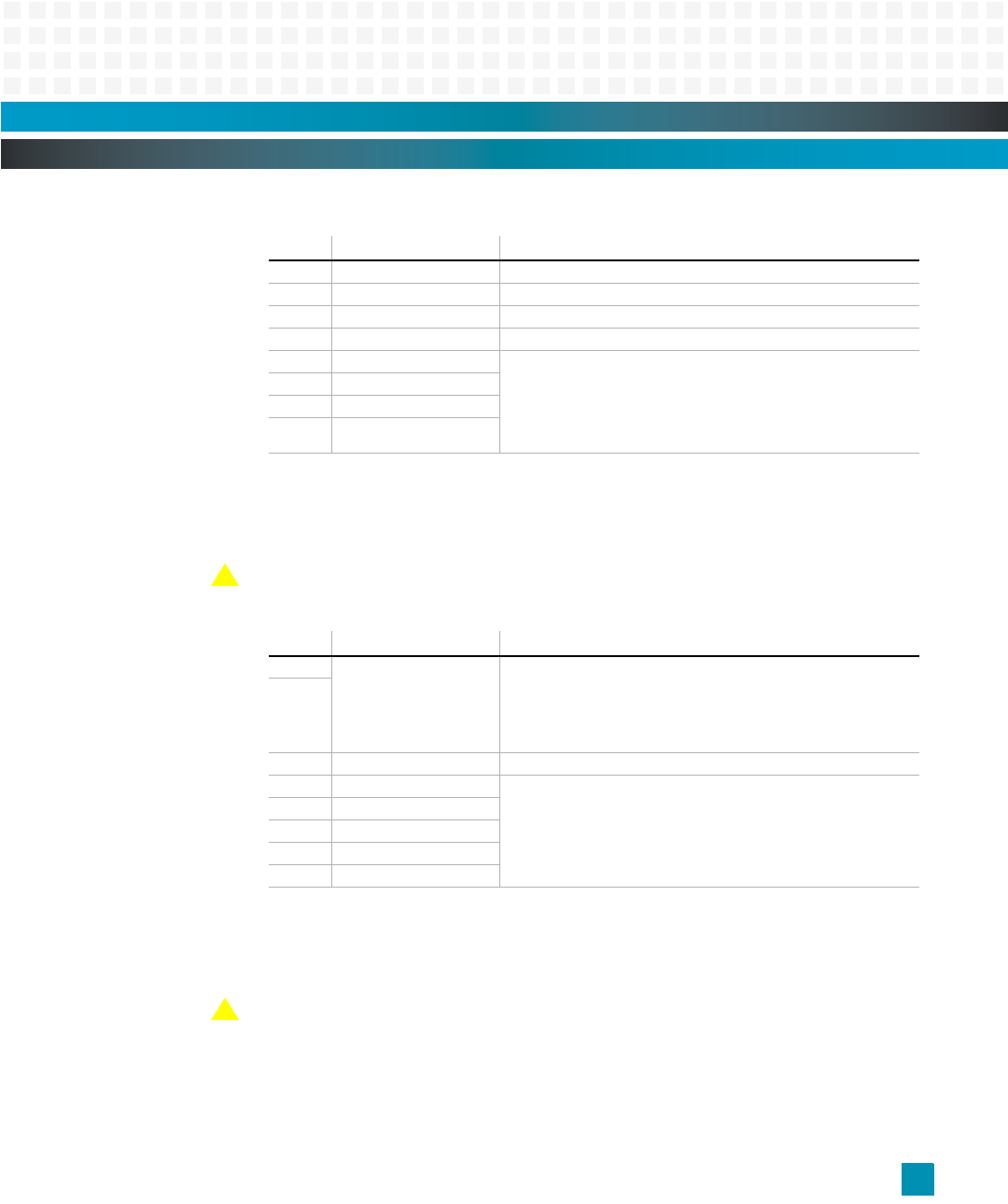

Register 5-20: RTM Control (0x68)

Cavium 1 C_MUL Clock Divisor Control

Use the C_MUL1 register to reduce the speed of the Cavium CN5860 processor 1 core.

Caution: Do not over-clock the Cavium frequency (bits 6:7 hard strapped).

Register 5-21: Cavium 1 C_MULL Clock Divisor Control (0x70)

Cavium 2 C_MUL Clock Divisor Control

Use the C_MUL2 register to reduce the speed of the Cavium CN5860 processor 2 core.

Caution: Do not over-clock the Cavium frequency (bits 6:7 hard strapped).

Bits: Function: Description:

70

60

50

4 RTMP RTM is Present

3 RTMID3 RTM Identification bits 3:0

0000 = Test RTM (factory only)

1000 = 20GbE I/O RTM

1100 = 18GbE and 2x10GbE I/O RTM

1010 = Storage RTM

2RTMID2

1RTMID1

0RTMID0

Bits: Function: Description:

7 CAVF Cavium Frequency resistor set bit (read-only)

00 600

01 750

10 800

11 reserved

6

5CMULOE C_MUL Output Enable

4 P1CMUL4 These bits drive directly to the Cavium 1. The core clock speed

is the number multiplied by 50 MHz. For example, the 800 MHz

core is set to 16(0x10).

3P1CMUL3

2P1CMUL2

1P1CMUL1

0P1CMUL0

!

!