Management Processor CPLD: MPC8548 PLD Register

10009109-01 ATCA-9305 User’s Manual

5-7

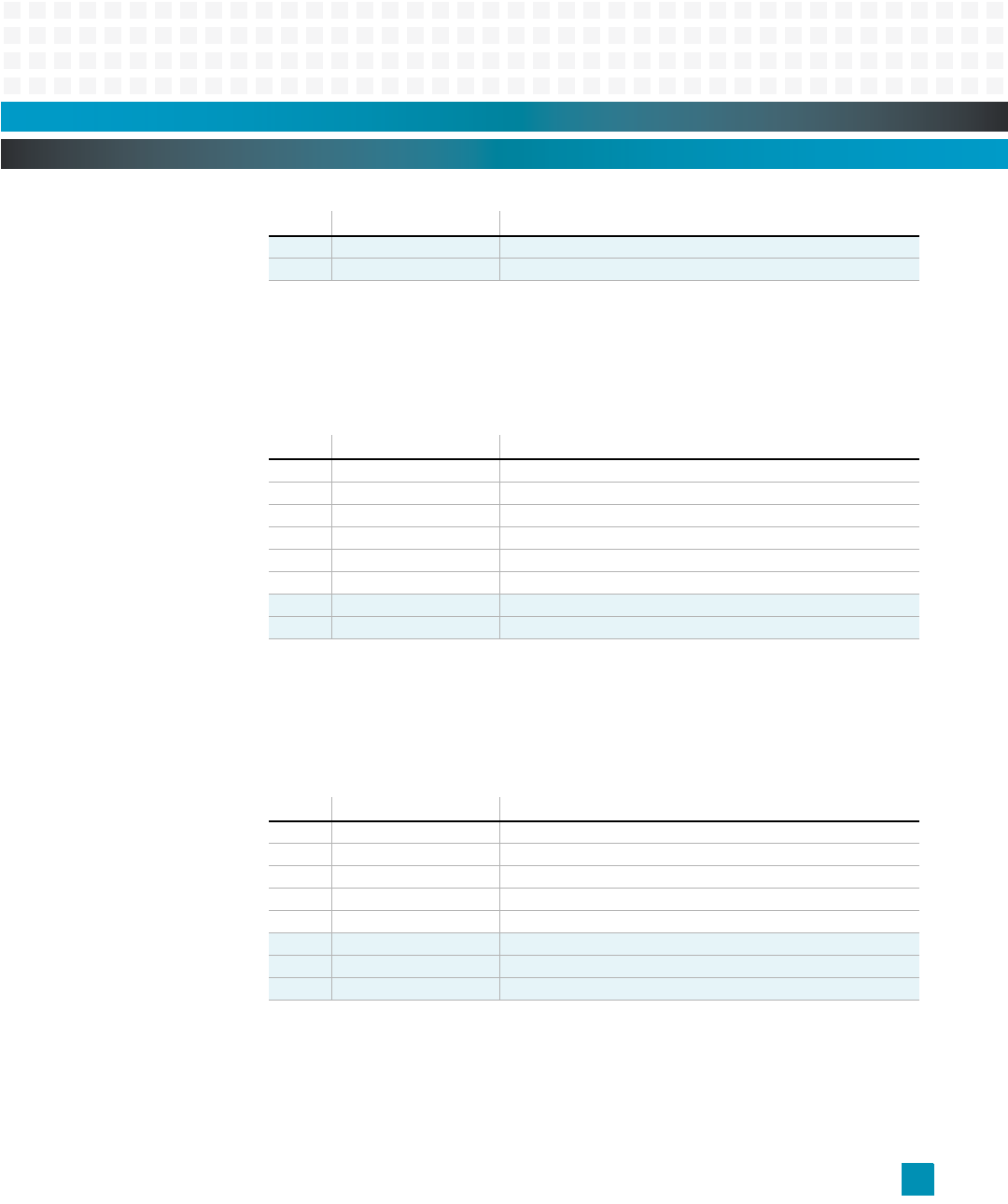

Reset Command 4

The write-only Reset Command 4 register forces one of several types of Cavium 2 resets, as

shown below. A reset sequence is first initiated by writing a one to a single valid bit, then the

PLD performs that particular reset, and the bit is automatically cleared.

Register 5-12: Reset Command 4 (0x30)

Reset Command 5

The write-only Reset Command 5 register forces one of several types of BCM5680x Ethernet

switch resets, as shown below. A reset sequence is first initiated by writing a one to a single

valid bit, then the PLD performs that particular reset, and the bit is automatically cleared.

Register 5-13: Reset Command 5 (0x34)

Reset Command Sticky #1

The read/write Reset Command Sticky #1 register forces one of several types of the group-

complex resets, as shown below. A reset sequence is first initiated by writing a one to one or

more bits, then the PLD performs that particular reset. The bit will persist until cleared.

1 reserved

0 reserved

Bits: Function: Description:

7 CAV2R Cavium 2 Reset

6 CAV2PR Cavium 2 PCI Reset

5 CAV2DR Cavium 2 DDR SDRAM Reset

4 CAV2F Cavium 2 4 MB Flash (Cavium local bus) reset

3 CAV2M3 Cavium 2 MIP3 reset

2 CAV2M4 Cavium 2 MIP4 reset

1 reserved

0 reserved

Bits: Function: Description:

7 SWIR Switch Reset

6 TSEC1R TSEC1 Ethernet to front panel PHY Reset

5 TSEC2R TSEC2 Ethernet to switch PHY Reset

4 FPIR FPI Ethernet to front panel PHY Reset

3 BCR Ethernet dual PHY to backplane Base Channel reset

2 reserved

1 reserved

0 reserved

Bits: Function: Description: (continued)