Management Processor CPLD: MPC8548 PLD Register

ATCA-9305 User’s Manual 10009109-01

5-10

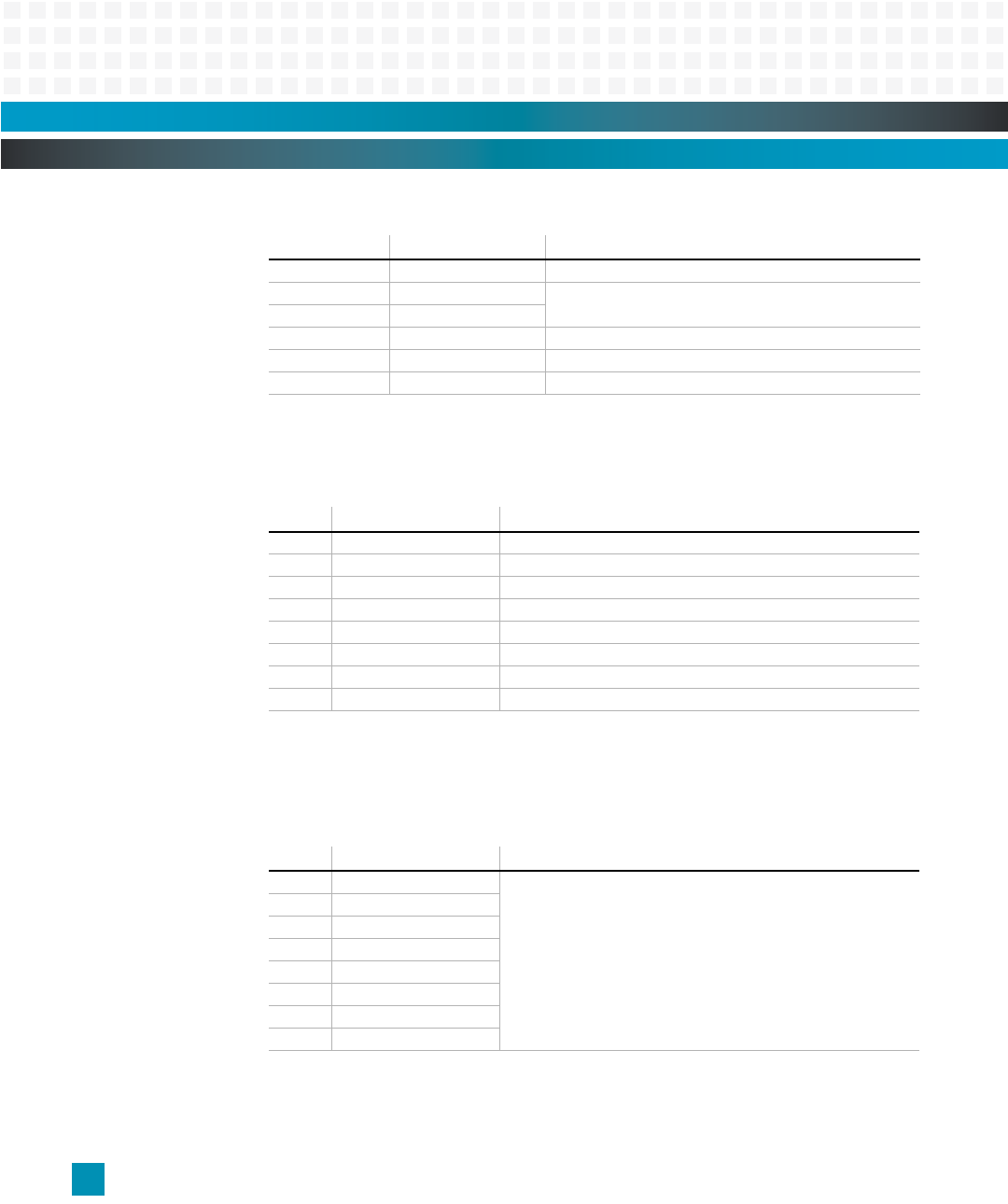

Table 5-2: Low Frequency Timer Settings

RTM GPIO State

This read-only register reads the current state of the GPIO pins.

Register 5-18: RTM GPIO State (0x60)

RTM GPIO Control

This register sets the state of the GPIO pins. These signals are implemented as open collec-

tor signals.

Register 5-19: RTM GPIO Control (0x64)

RTM Status

The RTM identification (ID) is determined by factory installed configuration resistors.

Frequency: Set Register: Comments:

0 Off Never interrupts

1 Hz 19999 (0x4E1F) These frequencies require the use of both registers

10 Hz 1999 (0x7CF)

100 Hz 199 (0xC7)

1 KHz 19 (0x13)

10 KHz 1 This equals two 50 μs time units (default)

Bits: Function: Description:

7RTM_GPIO 7

6RTM_GPIO 6

5RTM_GPIO 5

4RTM_GPIO 4

3RTM_GPIO 3

2RTM_GPIO 2

1RTM_GPIO 1

0RTM_GPIO 0

Bits: Function: Description:

7 RTM_GPIO 7 0 Causes the corresponding bit to be driven to 0

1 Tristates the signal; this will either be read by the RTM as a 1

or can be driven by the RTM to any value

6RTM_GPIO 6

5RTM_GPIO 5

4RTM_GPIO 4

3RTM_GPIO 3

2RTM_GPIO 2

1RTM_GPIO 1

0RTM_GPIO 0